|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

Przed lekturą zapoznaj się z tym rozdziałem.

Technika cyfrowa opiera się na tzw. algebrze Boole'a. Rozróżniamy w niej dwie wartości logiczne: prawdę (ang. true) i fałsz (ang. false). W urządzeniach elektronicznych wartości te będą reprezentowane przez poziomy napięć:

Na przykład:

Dla VCC = 1,8V (najniższe możliwe napięcie zasilania mikrokontrolerów Atmel):

Dla VCC = 2,7V (napięcie przy zasilaniu z dwóch akumulatorków paluszkowych):

Dla VCC = 5V (typowe napięcie pracy mikrokontrolera):

Napięcie o poziomie pośrednim traktowane jest jako nieokreślone i należy go unikać. W przeciwnym wypadku działanie układu będzie niestabilne.

Umówmy się, że poziomy logiczne będziemy oznaczali cyframi 0 (poziom niski) oraz 1 (poziom wysoki).

W algebrze Boole'a, podobnie jak w zwykłej algebrze, występują działania na wartościach logicznych, które będziemy nazywali funkcjami logicznymi. Poniżej przedstawiamy trzy podstawowe funkcje logiczne, które będziemy opisywali nazwami angielskimi, ponieważ tak jest przyjęte w literaturze fachowej, więc się przyzwyczajaj.

Pierwsza funkcja to NOT, czyli negacja lub zaprzeczenie logiczne. Tabelka logiczna jest następująca:

| a | NOT a |

| 0 | 1 |

| 1 | 0 |

Jest to funkcja jednoargumentowa. Zwraca zawsze wartość przeciwną logicznie do wartości swojego argumentu.

Drugą funkcją jest OR, czyli alternatywa lub suma logiczna. W przeciwieństwie do funkcji NOT funkcja OR wymaga co najmniej dwóch argumentów.

| a | b | a OR b |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Funkcja OR przybiera wartość wysoką 1 tylko wtedy, gdy jeden z jej argumentów ma wartość 1. Wartość niską 0 funkcja OR przyjmuje tylko wtedy, gdy wszystkie jej argumenty mają wartość 0. Zwróć uwagę, że funkcja OR jest podobna do operacji dodawania. Suma dwóch liczb nieujemnych jest równa zero, gdy obie liczby mają wartość 0 (0 + 0 = 0; 0 OR 0 = 0). Suma dwóch liczb nieujemnych jest różna od zera, jeśli co najmniej jedna z tych liczb jest różna od zera. Funkcja może mieć więcej niż dwa argumenty:

| a | b | c | a OR b OR c |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Trzecią funkcją jest AND, czyli koniunkcja lub iloczyn logiczny. Funkcja AND jest również co najmniej dwuargumentowa.

| a | b | a AND b |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Funkcja AND przyjmuje poziom wysoki 1 tylko wtedy, gdy wszystkie jej argumenty mają poziom 1. W przeciwnym razie funkcja AND ma poziom niski 0. Takie zachowanie podobne jest to iloczynu liczb: iloczyn dwóch liczb jest różny od zera tylko wtedy, gdy obie liczby są różne od zera (1 AND 1 = 1). W przeciwnym razie iloczyn jest równy zero.

Aby zrealizować dowolną funkcję logiczną, potrzebne są tylko dwie podstawowe funkcje: NOT + AND lub NOT + OR. Dzieje się tak za sprawą tzw. praw De Morgana:

| NOT(a AND b) = (NOT

a) OR (NOT b) NOT(a OR b) = (NOT a) AND (NOT b) |

Prawa te pozwalają wyrażać koniunkcję za pomocą negacji oraz alternatywy. Również odwrotnie, pozwalają one wyrażać alternatywę za pomocą koniunkcji i negacji. Wprowadźmy dwie dodatkowe funkcje logiczne:

| a NAND b = NOT(a AND b) oraz a NOR b = NOT(a OR b) |

|

|

Funkcja NOR jest zaprzeczoną sumą logiczną. Jest prawdziwa, jeśli jej wszystkie argumenty są fałszywe. W przeciwnym razie funkcja NOR zwraca fałsz.

Funkcje te są uniwersalne, ponieważ przy ich pomocy możemy wyrazić każdą z pozostałych funkcji logicznych:

| NOT a | a NAND a | a NOR a |

| a OR b | (a NAND a) NAND (b NAND b) | (a NOR b) NOR (a NOR b) |

| a AND b | (a NAND b) NAND (a NAND b) | (a NOR a) NOR (b NOR b) |

Realizacją funkcji logicznej w technice cyfrowej jest element elektroniczny zwany bramką (ang. gate). Bramka cyfrowa posiada wejścia oraz wyjście. Wejścia odpowiadają argumentom funkcji logicznej realizowanej przez bramkę, a wyjście odpowiada wartości tej funkcji.

Stan wyjścia bramki zależy od stanu sygnałów na jej wejściach oraz od realizowanej przez nią funkcji logicznej. W technice cyfrowej napięcia wejściowe oraz wyjściowe przyjmują dwa różne poziomy: niski 0 (0...0,8V) i wysoki 1 (1,8...5V). Pomiędzy tymi poziomami jest przerwa, która pozwala układom cyfrowym rozróżnić te stany pomiędzy sobą. Napięcie o wartości leżącej w przerwie pomiędzy stanem 0 a 1 oznacza nieokreślony poziom logiczny i należy go unikać, ponieważ układ cyfrowy może działać wtedy wadliwie.

Wyjścia bramek można łączyć z wejściami innych bramek logicznych (samych wyjść nie wolno ze sobą łączyć, ponieważ prowadzi to do zwarcia i w konsekwencji do uszkodzenia bramki – wyjątkiem są specjalne bramki z wyjściami typu otwarty kolektor, co opiszemy później) – w ten sposób powstaje sieć logiczna realizująca złożoną funkcję logiczną. Każde wejście bramki dołączone do wyjścia innej bramki pobiera z niej pewien prąd elektryczny. Wyjścia bramek mogą dostarczyć tylko określoną ilość prądu. Wynika z tego, iż do typowego wyjścia można podłączyć ograniczoną ilość wejść innych bramek. Parametr ten nosi nazwę obciążalności wyjścia bramki. Zwykle przyjmuje się go na poziomie 10 (należy sprawdzić w danych producenta) dla zwykłych bramek oraz 30 dla bramek o zwiększonej mocy wyjściowej.

Obciążalności wyjściowej bramki nie należy przekraczać, gdyż może to spowodować niestabilność sieci logicznej (kłopoty z utrzymaniem odpowiedniego poziomu napięcia wyjściowego przez przeciążoną bramkę), a nawet spalenie niektórych jej elementów.

Uwaga:

Poziom napięcia wyjściowego bramki jest funkcją logiczną Boole'a poziomu logicznego napięć wejściowych. Napięcie na wyjściu nie zmienia się natychmiast po zmianie poziomu napięć wejściowych, lecz po pewnym czasie – typowo po 10 ns (należy sprawdzić w danych producenta). Jest to spowodowane tym, iż tranzystory wewnątrz bramki muszą się odpowiednio przełączyć, a to wymaga czasu.

Bramki cyfrowe oznaczamy na schematach elektrycznych za pomocą odpowiednich symboli graficznych (stosujemy ogólnie przyjęte oznaczenia amerykańskie), które musisz sobie przyswoić. Poniżej przedstawione są te symbole wraz z krótkim opisem.

Bramka NOT |

|

Bramka NOT często nazywana jest negatorem lub inwerterem, ponieważ "odwraca" poziom napięcia logicznego z wejścia. Symbol kółeczka na wyjściu lub wejściu oznacza negację sygnału. Symbol inwertera można również narysować jak poniżej:

Bramka

NOT |

|

Bramka AND |

|

Bramki logiczne mogą posiadać więcej niż dwa wejścia. Na przykład poniżej przedstawiamy bramkę AND trójwejściową.

| Trójwejściowa bramka AND  |

|

Bramka OR |

|

Bramka NAND |

|

|||||||||||||||

Bramka NOR |

|

Poniżej przedstawiamy sposoby uzyskania podstawowych funkcji logicznych przy pomocy bramek uniwersalnych NAND i NOR.

Bramka NOT |

= | z

bramki NAND |

= | z

bramki NOR |

Bramka OR |

= | z bramek NAND |

= | z bramek NOR |

Bramka AND |

= | z bramek NAND |

= | z bramek NOR |

Musimy jednakże pamiętać, iż takie rozwiązanie jest gorsze od zastosowania właściwej bramki logicznej – zwiększa się obciążenie wyjść bramek sterujących (w niektórych układach łączone ze sobą dwa wejścia bramki) oraz zwiększa się czas propagacji (bramki pracują szeregowo).

Bramki buforowe stosowane są do wzmacniania sygnałów cyfrowych lub do sterowania pracą różnych układów (np. wyświetlaczem LED). Nie powodują one zmiany sygnału wejściowego (poza pewnym opóźnieniem spowodowanym czasem propagacji).

Bramka buforowa |

|

Czasem występuje potrzeba połączenia ze sobą wyjść kilku bramek. Ze zwykłymi bramkami tak nie można postępować, ponieważ prowadzi to do zwarcia i w konsekwencji do uszkodzenia bramki. Dlatego produkuje się bramki, których wyjście zawiera tranzystor z otwartym kolektorem (ang. open collector output). Wygląda to następująco:

Tranzystor wyjściowy pracuje w dwóch trybach:

Wyjścia bramek OC łączy się ze sobą i podłącza do plusa zasilania poprzez opornik 1k:

W miejscu połączenia wyjść bramek powstaje tzw. logiczny iloczyn montażowy lub galwaniczny (ang. wired AND). Oznacza to, iż na wyjściu Y panuje stan wysoki, jeśli wszystkie tranzystory wyjściowe bramek pracują w stanie wysokim, tzn. ich złącza emiter-kolektor nie przewodzą. W takim przypadku opornik wymusza wysoki poziom napięcia. Jeśli w dowolnej bramce tranzystor końcowy przejdzie w stan niski, to zwiera wyjście do masy i napięcie wyjściowe spada do poziomu niskiego.

Stanem nieaktywnym bramki jest tutaj stan wysoki.

|

|

W roku 1958 udało się umieścić na jednej płytce krzemu kilka tranzystorów. W ten sposób powstał pierwszy układ scalony (ang. integrated circuit). Dzięki nim urządzenia elektroniczne można było zminiaturyzować. Dzisiejsze układy scalone mogą zawierać miliony tranzystorów. Ich wykonanie w wersji dyskretnej (z pojedynczych tranzystorów) byłoby niemożliwe, np. twój telefon komórkowy, który bez problemu mieścisz w kieszeni, miałby rozmiar 4-ro piętrowego bloku.

Bramki cyfrowe zbudowane są z kilku tranzystorów. Np. popularna bramka NAND posiada następujący schemat wewnętrzny:

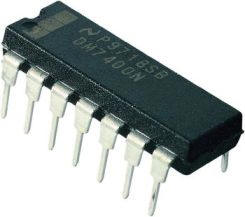

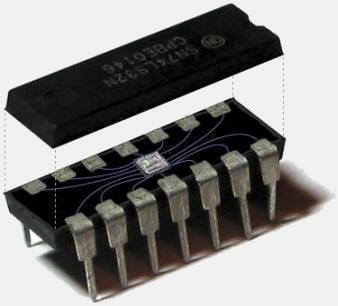

Zawiera zatem cztery tranzystory (jeden dwuemiterowy), trzy diody i cztery oporniki. Gdybyśmy chcieli budować urządzenia cyfrowe z tranzystorów, byłyby duże i skomplikowane. Tymczasem układ scalony zawierający 4 takie bramki NAND jest mały i łatwy w zastosowaniu:

|

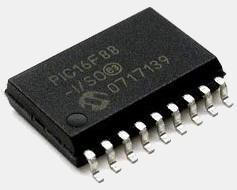

Z punktu widzenia użytkownika układ scalony jest malutkim pudełkiem, z którego wyprowadzono końcówki.

|

|

|

Wewnątrz tego pudełka znajduje się malutka płytka, na której utworzona jest struktura układu scalonego. Za pomocą małych drucików końcówki układu scalonego połączone są z odpowiednimi punktami tej struktury.

Funkcje końcówek zależą od rodzaju układu scalonego. Musisz poznać sposób ich numerowania. Zwróć uwagę, iż na obudowie znajduje się małe wycięcie lub mała dziurka. Układ ustawiamy nóżkami w dół, tak aby wcięcie na obudowie znalazło się po stronie lewej (lub punkt po lewej stronie u dołu). Wtedy numeracja nóżek rozpoczyna się od lewego dolnego rogu i biegnie wokół układu scalonego. Poniżej przedstawiamy widok z góry układu o 14 wyprowadzeniach.

Bramki cyfrowe są umieszczane w układach scalonych, które produkuje wiele różnych firm na całym świecie. Najpopularniejsze serie to TTL (bramki zbudowane z tranzystorów bipolarnych, obecnie buduje się również z tranzystorów polowych jako nowoczesne zamienniki przestarzałych układów bipolarnych) oraz CMOS (bramki zbudowane z tranzystorów polowych).

| Parametr | TTL | CMOS | HCT/ACT |

| Zasilanie | 5V | 3...15V | 4,5...5,5V |

| Poziom 0 | 0,4...0,8V | 0V | 0,1...0,8V |

| Poziom 1 | 2...5V | VDD | 2...4,9V |

| Czas propagacji | 1,5...3 ns | 30 ns | 7 ns |

| Obciążalność wyjść | 10 | duża | 4000 |

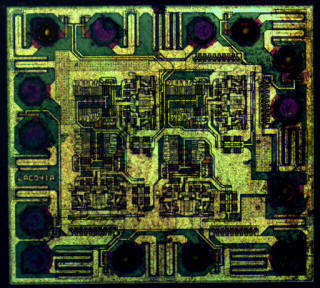

Produkowane są również zastępniki układów TTL wykonane w technologii HCT (szybkie układy logiczne CMOS), które nie ustępują szybkością układom TTL przy jednoczesnym obniżeniu poboru mocy. Temat ten jest dosyć rozległy i warto go opanowywać stopniowo w miarę potrzeb. Układy CMOS szczególnie nadają się do zasilania bateryjnego, gdyż pobierają bardzo mały prąd zasilający. Nie będziemy się tutaj wgłębiać w wewnętrzną budową bramek cyfrowych, ponieważ jest to zagadnienie skomplikowane i w sumie nam niezbyt potrzebne. Musimy jedynie znać właściwości bramek oraz ich parametry elektryczne. Poniżej przedstawiamy obraz płytki krzemowej, która znajduje się wewnątrz układu SN7400 (cztery bramki NAND). Na płytce tej wytworzone są w procesie produkcyjnym tranzystory oraz połączenia miedzy nimi.

Gdy umiemy już odczytywać numery wyprowadzeń układów scalonych, możemy zdefiniować ich zawartość. Poniżej przedstawiamy definicje wyprowadzeń kilku układów cyfrowych zawierających podstawowe bramki logiczne. Są to układy TTL serii SN74xx oraz CMOS serii CD40xx. GND oznacza masę dla TTL (minus zasilania), VSS dla CMOS. VCC oznacza napięcie zasilające układ scalony TTL (+5V), VDD dla CMOS. Wiedza ta pozwala na samodzielne konstruowanie prostych urządzeń cyfrowych. Układy zestawiliśmy, tak aby w obu seriach otrzymać funkcjonalne odpowiedniki. Dlatego kolejność numeracji układów CMOS nie jest zachowana.

| Układy TTL serii SN74xx | Układy CMOS serii CD40xx |

| Brak odpowiednika TTL |

CD4000 2 3–wejściowe bramki NOR i inwerter  |

|

SN7400 4 2–wejściowe bramki uniwersalne NAND  |

CD4011 4 2–wejściowe bramki uniwersalne NAND  |

|

SN7401 4 2–wejściowe bramki uniwersalne NAND z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7402 4 2–wejściowe bramki uniwersalne NOR  |

CD4001 4 2–wejściowe bramki uniwersalne NOR  |

|

SN7403 4 2–wejściowe bramki uniwersalne NAND z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7404 6 inwerterów  |

CD4009 6 inwerterów  |

|

SN7405 6 inwerterów z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7406 6 inwerterów z wyjściami wysokonapięciowymi typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7407 6 wzmacniaczy buforowych z wyjściami typu otwarty kolektor  |

CD4010 6 wzmacniaczy buforowych  |

|

SN7408 4 2–wejściowe bramki AND  |

CD4081 4 2–wejściowe bramki AND  |

|

SN7409 4 2–wejściowe bramki AND z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7410 3 3–wejściowe bramki uniwersalne NAND  |

CD4023 3 3–wejściowe bramki uniwersalne NAND  |

|

SN7411 3 3–wejściowe bramki AND  |

CD4073 3 3–wejściowe bramki AND  |

|

SN7412 3 3–wejściowe bramki uniwersalne NAND z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7415 3 3–wejściowe bramki AND z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7420 2 4–wejściowe bramki uniwersalne NAND  |

CD4012 2 4–wejściowe bramki uniwersalne NAND  |

|

SN7422 2 4–wejściowe bramki uniwersalne NAND z wyjściami typu otwarty kolektor  |

Brak odpowiednika CMOS |

|

SN7437 4 2–wejściowe bramki buforowe NAND  |

Brak odpowiednika CMOS

|

|

SN7440 2 4–wejściowe bramki buforowe NAND  |

Brak odpowiednika CMOS |

|

SN7421 2 4–wejściowe bramki AND  |

CD4082 2 4–wejściowe bramki AND  |

| Brak odpowiednika TTL |

CD4002 2 4–wejściowe bramki uniwersalne NOR  |

| Brak odpowiednika TTL |

CD4072 2 4–wejściowe bramki OR  |

|

SN7427 3 3–wejściowe bramki uniwersalne NOR  |

CD4025 3 3–wejściowe bramki uniwersalne NOR  |

| Brak odpowiednika TTL |

CD4075 3 3–wejściowe bramki OR  |

|

SN7430 1 8–wejściowa bramka uniwersalna NAND  |

CD4068 1 8–wejściowa bramka uniwersalna NAND  |

| Brak odpowiednika TTL |

CD4078 1 8–wejściowa bramka uniwersalna NOR  |

|

SN7432 4 2–wejściowe bramki OR  |

CD4071 4 2–wejściowe bramki OR  |

Więcej na temat układów cyfrowych znajdziesz w osobnym artykule dostępnym w naszym serwisie. Zapraszamy.

Do jednego wyjścia bramki można podłączyć kilka wejść innych bramek. Musimy tylko pamiętać, aby nie przekroczyć obciążalności wyjścia bramki. Typowe wyjście bramki TTL może wysterować około 10 wejść innych bramek TTL. Do bramek CMOS reguła ta się nie odnosi, ponieważ pobierają one bardzo mały prąd wejściowy – mówimy, iż posiadają dużą oporność wejściową.

Nieużywane wejścia bramek należy podłączyć poprzez opornik 1kΩ (jeśli możemy zagwarantować, iż napięcie VCC nie przekroczy 5,5V, to wejście można połączyć bezpośrednio) do zasilania +5V (bramki AND i NAND) lub bezpośrednio do masy (bramki OR i NOR). Nie wolno pozostawiać wejścia "wiszącego", ponieważ powoduje to pogorszenie warunków pracy bramki (zwiększa się czas propagacji oraz zmniejsza się odporność na zakłócenia) i w konsekwencji może powodować błędy w działaniu całego urządzenia cyfrowego.

Nie wolno łączyć ze sobą wyjść bramek, gdyż prowadzi to do zwarcia i w konsekwencji może uszkodzić układ cyfrowy. Jedynym wyjątkiem są bramki z wyjściem typu otwarty kolektor, które są specjalnie zaprojektowane do takich połączeń. Pomówimy o nich przy innej okazji.

Z diodami LED spotkaliśmy się w jednym z poprzednich rozdziałów. Powtórzmy sobie podstawowe wiadomości.

Dioda LED (ang. Light Emitting Diode) jest elementem elektronicznym, który przewodzi prąd tylko w jednym kierunku. Gdy prąd o odpowiednim natężeniu przepływa przez diodę LED, emituje ona światło. Kolor świecenia zależy od materiału użytego do konstrukcji diody.

Diody LED bardzo często wykorzystywane są w technice cyfrowej jako różnego rodzaju wskaźniki i oświetlenie – np. zegary wyświetlają przy ich pomocy cyfry czasu i daty, telefony komórkowe używają ich do podświetlania swoich ekranów i klawiatur. Stosując diody LED, należy pamiętać o rzeczach następujących:

Zwykłe diody o średnicach 3/5mm (najbardziej popularne cenowo) pobierają prąd IF = 10...20mA. Jeśli chcemy uzyskać niezawodność świecenia, to obniżamy ten prąd do około 15mA (tyle może na wyjściu dostarczyć standardowa bramka TTL, bramki HCT mogą dostarczać prąd 25...75mA). Napięcie UF określamy z poniższej tabelki:

| Rodzaj diody LED | Napięcie UF | Prąd IF |

| zwykłe, czerwone | 1,7...1,8V | 15mA |

| jasne, czerwone wysokowydajne, czerwone niskoprądowe, czerwone |

1,9V | 15mA |

| pomarańczowe i żółte | 2V | 15mA |

| zielone | 2,1V | 15mA |

| jasne, białe jasne, zielone bez żółtozielonego niebieskie zwykłe |

3,4V | 12mA |

| jasne, niebieskie | 4,6V | 10mA |

Do naszych celów najlepsze będą diody o UF = 1,7V ... 2,1V. Diody o wyższym napięciu wymagają tranzystora sterującego, który zapewni im odpowiednie warunki zasilania (w bramkach TTL, układ HCT bez problemy wysteruje taką diodę). Diodę LED można podłączyć do wyjścia bramki TTL na dwa sposoby. W obu przypadkach należy odpowiednio dobrać opór ograniczający prąd diody LED. Poniżej przedstawiamy odpowiednie wzory obliczeniowe dla bramek TTL (układy HCT dają napięcie wyjściowe około 4,5V w stanie wysokim 1 i około 0,1V w stanie niskim 0):

| Dioda świeci

przy stanie wysokim na wyjściu bramki

|

Dioda świeci

przy stanie niskim na wyjściu bramki

|

|

|

| Dla diody czerwonej o UF = 1,7V i IF = 0,015A otrzymamy: | |

|

|

Dla wersji pierwszej napięcie 3,5V jest napięciem wyjściowym bramki TTL w stanie wysokim (dla HCT przyjmuj 4,5V). Napięcie to rozkłada się na opornik R oraz diodę LED. Gdy odejmiemy od niego napięcie UF diody LED, to pozostanie napięcie tylko na oporniku R. Dzieląc to napięcie przez pożądany prąd IF otrzymujemy wartość oporu opornika R, który należy w tym układzie zastosować.

W praktyce w obu przypadkach stosuje się oporniki 270...470Ω, ponieważ współcześnie produkowane diody LED świecą bardzo jasno nawet przy małym prądzie.

Dla wersji drugiej jest podobnie. Napięcie 4,6V jest napięciem zasilania pomniejszonym o napięcie 0,4V (dla HCT przyjmuj około 4,9V, ponieważ na wyjściu w stanie niskim jest 0,1V), które pojawia się na wyjściu bramki w stanie niskim.

Powyższe dwa układy można połączyć w jeden – górna dioda LED będzie świeciła w stanie niskim, a dolna dioda LED będzie świeciła w stanie wysokim.

Najbardziej popularną bramką cyfrową TTL jest bramka NAND. Układ SN7400 (74HCT00) zawiera cztery bramki dwuwejściowe NAND.

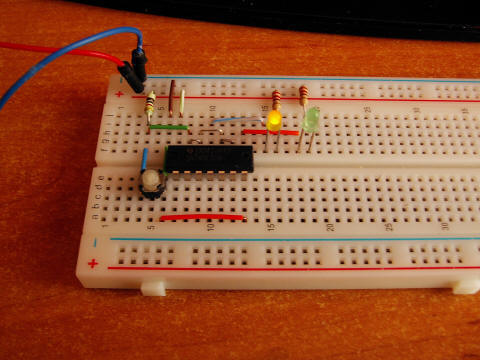

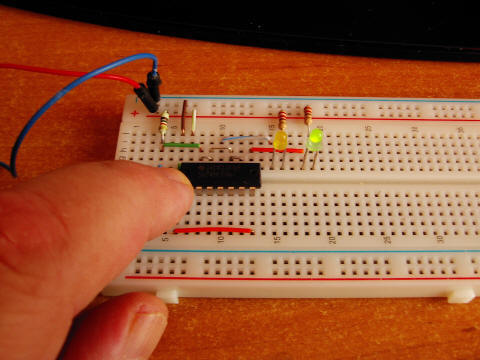

Zaprojektujemy teraz prosty obwód zbudowany z dwóch bramek NAND (bramki pracują jako inwertery, możemy też zamiast bramek NAND zastosować bramki NOT typu SN7404/74HCT04). Schemat jest następujący:

|

Spis elementów:

Zamiast mikroprzełącznika możesz |

||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||

|

Za pomocą podanych wcześniej wzorów obliczamy wartości oporów R1 i R2.

Przyjmujemy R1 = 180Ω

Przyjmujemy R2 = 100Ω

Jeśli nie posiadasz dokładnie takich oporników, możesz po prostu zastosować dwa oporniki większe, np. 220Ω lub 270Ω. Przy jasnych diodach LED różnica nie będzie wcale widoczna.

Gdy podłączysz zasilanie, wejścia bramek NAND będą się znajdowały w stanie wysokim 1, ponieważ są podłączone poprzez opornik 1k do plusa zasilania. Zatem na ich wyjściach pojawi się stan niski 0. W stanie niskim będzie świeciła tylko dioda żółta. Gdy wciśniesz przycisk, zewrze on wejścia bramek NAND do masy, co jest równoważne podaniu na nie stanu niskiego 0. Na wyjściach bramek pojawi się stan wysoki. W stanie wysokim świeci tylko dioda zielona.

Problem pojawia się, gdy chcemy sterować elementem pobierającym większy prąd niż może dostarczyć bramka. Nie wolno go wtedy podłączać bezpośrednio do wyjścia bramki, gdyż może to spowodować jej uszkodzenie. W takim przypadku zaprzęgamy do pracy tranzystor mocy.

|

Spis elementów:

Zamiast mikroprzełącznika możesz |

|||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||

|

Gdy włączysz zasilanie, wejścia bramki NAND będą się znajdowały w stanie wysokim 1, ponieważ są podłączone do plusa zasilania poprzez opornik 1k. Na wyjściu bramki panuje stan niski 0 . Stan ten jest wymuszany na bazie tranzystora. Tranzystor jest zatkany i nie przewodzi prądu w obwodzie kolektor–emiter, zatem żarówka nie świeci. Jeśli teraz naciśniesz przełącznik, to zewrze on wejścia bramki do masy, czyli wymusi na nich stan niski 0. Spowoduje to pojawienie się stanu wysokiego 1 na wyjściu bramki i wysterowanie bazy tranzystora. W obwodzie baza–emiter popłynie prąd, który z kolei wymusi prąd w obwodzie kolektor–emiter. Tranzystor zacznie przewodzić i żarówka się zaświeci. Tranzystor pełni tutaj rolę przełącznika oraz wzmacniacza prądu. Z wyjścia bramki będzie pobierany niewielki prąd (około 20mA).

Jeszcze lepszym rozwiązaniem jest zastosowanie tranzystora unipolarnego MOSFET-N. Tranzystor nie będzie praktycznie obciążał wyjścia bramki, ponieważ posiada bardzo dużą oporność wejściową i sterowanie odbywa się za pomocą napięć.

|

Spis elementów:

Zamiast mikroprzełącznika możesz |

|||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||

|

Jeśli stosujesz zwykły układ TTL (SN7400), to napięcie zasilające musi wynosić co najmniej 4,5V (nowe baterie lub dobrze naładowane akumulatory). W przeciwnym razie bramka NAND nie wysteruje tranzystora MOSFET-N.

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.