|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

If you use Microchip copyrighted material solely for educational (non-profit) purposes falling under the “fair use” exception of the U.S. Copyright Act of 1976 then you do not need Microchip’s written permission. For example, Microchip’s permission is not required when using copyrighted material in: (1) an academic report, thesis, or dissertation; (2) classroom handouts or textbook; or (3) a presentation or article that is solely educational in nature (e.g., technical article published in a magazine).

https://www.microchip.com/about-us/legal-information/copyright-usage-guidelines

Zestaw rejestrów o szybkim dostępie składa się z 32 8-bitowych roboczych rejestrów ogólnego przeznaczenia o czasie dostępu w jednym cyklu zegara. Oznacza to, iż w czasie pojedynczego cyklu zegara JAL (Jednostka Arytmetyczno Logiczna, ang. Arithmetic Logic Unit, ALU) wykonuje całą operację. Ze zestawu rejestrów pobierane są dwa argumenty, wykonywana jest na nich operacja, a wynik zostaje z powrotem umieszczony w zestawie rejestrów – w jednym cyklu zegara.

Dwa z 32 rejestrów mogą być używane jako 16-bitowy wskaźnik przy pośrednim dostępie do pamięci. Wskaźnik ten ma nazwę Z i może adresować zestaw rejestrów oraz pamięć FLASH programu.

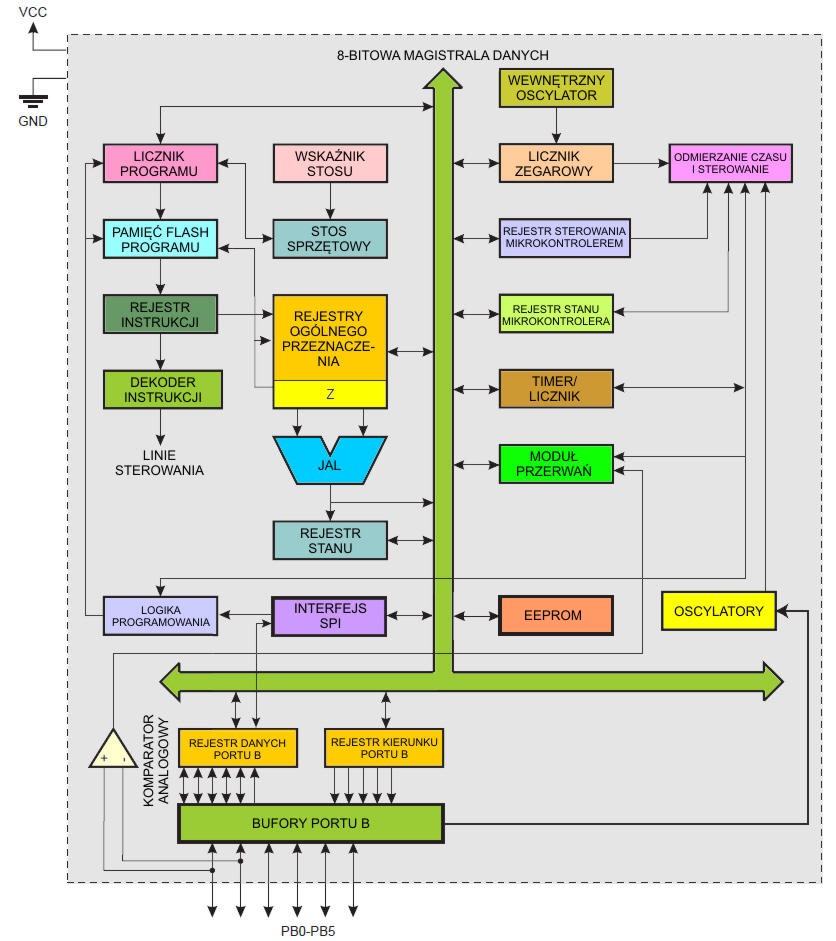

JAL wykonuje operacje arytmetyczne i logiczne pomiędzy rejestrami lub pomiędzy stałą a rejestrem. W JAL są również wykonywane operacje na pojedynczym rejestrze. Poniższy rysunek przedstawia architekturę RISC AVR mikrokontrolera ATtiny11/12 (ATtiny11 nie posiada SPI oraz pamięci EEPROM).

AVR wykorzystuje koncepcję architektury harwardzkiej z rozdzielonymi pamięciami i magistralami dla pamięci programu i danych. Pamięć programu jest odczytywana z dwuetapowym nakładkowaniem. Gdy wykonywana jest jedna instrukcja, następna instrukcja w tym samym czasie zostaje pobrana z pamięci programu. Takie rozwiązanie umożliwia wykonywanie instrukcji w każdym cyklu zegarowym. Pamięć programu jest programowalną pamięcią FLASH.

Za pomocą instrukcji skoków względnych i względnych wywołań podprogramów cała przestrzeń adresowa 512 słów jest bezpośrednio dostępna. Wszystkie instrukcje AVR posiadają pojedynczy format 16-bitowy, co oznacza, iż każdy adres w pamięci programu wskazuje pojedynczą, 16-bitową instrukcję.

Podczas przerwań i wywołań podprogramów adres powrotny licznika programu (ang. program counter, PC) zostaje zapisany na stosie. Stos jest stosem sprzętowym o pojemności 3 adresów dedykowanym dla podprogramów i przerwań.

Pamięć we/wy zawiera 64 adresy dla funkcji peryferyjnych mikroprocesora, takich jak rejestry sterujące, timer/licznik oraz inne funkcje we/wy. Przestrzenie pamięci w architekturze AVR są liniowymi i regularnymi odwzorowaniami w pamięci.

Elastyczny moduł przerwań posiada swoje rejestry sterujące w przestrzeni we/wy z dodatkowym bitem globalnego uaktywniania przerwań w rejestrze stanu. Wszystkie przerwania posiadają oddzielne wektory przerwań w tablicy wektorów przerwań umieszczonej na początku pamięci programu. Przerwania posiadają priorytety zgodne z położeniami ich wektorów przerwań. Im niżej w tablicy znajduje się dany wektor, tym wyższy priorytet posiada jego przerwanie.

Poniższy rysunek przedstawia strukturę 32 rejestrów ogólnego przeznaczenia w mikroprocesorze AVR:

Wszystkie instrukcje operujące na rejestrach w zestawie instrukcji ATtiny11/12 posiadają bezpośredni dostęp w jednym cyklu zegarowym do wszystkich rejestrów. Jedynymi wyjątkami jest pięć instrukcji arytmetycznych i logicznych wykonujących operacje pomiędzy stałą a rejestrem (SBCI, SUBI, CPI, ANDI i ORI) oraz instrukcja LDI, ładująca daną natychmiastową. Instrukcje te mają dostęp do drugiej połowy rejestrów w zestawie – R16...R31. Ogólne operacje odejmowania, porównywania, funkcji logicznych pomiędzy dwoma rejestrami lub operacje na pojedynczych rejestrach odnoszą się do całego zestawu rejestrów.

Rejestry R30 i R31 tworzą 16-bitowy wskaźnik (wskaźnik Z), który jest używany przy pośrednim dostępie do pamięci FLASH oraz do zestawu rejestrów. Gdy wykonywany jest dostęp do zestawu rejestrów, zawartość R31 (górny bajt indeksu Z) jest ignorowana przez mikroprocesor.

Wydajna jednostka arytmetyczno logiczna AVR działa z bezpośrednim połączeniem z wszystkimi 32 rejestrami roboczymi ogólnego przeznaczenia. W czasie pojedynczego cyklu zegarowego wykonywane są operacje JAL pomiędzy rejestrami z zestawu. Operacje JAL są podzielone na trzy główne kategorie – arytmetyczne, logiczne i bitowe. Niektóre mikrokontrolery z rodziny AVR posiadają również instrukcje mnożenia sprzętowego w części arytmetycznej JAL. Zobacz do ogólnej listy rozkazów AVR.

Mikrokontroler ATtiny11/12 zawiera 1KB wbudowanej w układ pamięci FLASH na przechowywanie programu. Ponieważ wszystkie instrukcje w tym modelu mikrokontrolera są pojedynczymi słowami 16-bitowymi, pamięć FLASH została zorganizowana w 512 słów. Pamięć FLASH wytrzymuje co najmniej 1000 cykli zapisu/kasowania.

Rejestr licznika programu (ang. program counter, PC) ma długość 9 bitów w ATtiny11/12, co pozwala na zaadresowanie 512 słów pamięci programu FLASH. Szczegóły znajdziesz w rozdziale "Programowanie pamięci".

Mikrokontroler RISC AVR ATtiny11/12 wspiera zaawansowane i efektywne tryby adresowania. Ten podrozdział opisuje te z trybów, które są używane w ATtiny11/12 (inne mikrokontrolery AVR mogą posiadać ich więcej). Na rysunkach OP oznacza część operacyjną słowa kodu instrukcji (czyli bity, których zawartość określa rodzaj instrukcji do wykonania). Ponieważ w różnych rozkazach bity te znajdują się w różnych miejscach kodu, dla uproszczenia nie wszystkie rysunki pokazują dokładne położenie bitów adresujących (więcej informacji znajdziesz w ogólnej liście rozkazów AVR).

Rr –

Rejestr źródłowy

Rd –

Rejestr docelowy

Tryb dotyczy instrukcji RJMP i RCALL. Pole k jest zwiększane o 1 i dodawane do aktualnej zawartości licznika rozkazów, a wynik zostaje umieszczony w liczniku rozkazów. W efekcie mikrokontroler wykona instrukcję spod adresu PC + k + 1. Pole k jest traktowane jako liczba ze znakiem w kodzie U2. Posiada ono długość 12 bitów. Zakres przesunięcia wynosi od -2048 do 2047.

Tryb ten odnosi się do instrukcji LPM. Adres bajtu stałej jest określany przez zawartość rejestru Z. Pamięć programu zorganizowana jest w słowa 16-bitowe, zatem każda jej komórka składa się z dwóch bajtów: młodszego (ang. Less Significant Bajt, LSB) oraz starszego (ang. More Significant Byte, MSB). 15 starszych bitów rejestru Z stanowi adres komórki ze stałą, czyli adres słowa 16-bitowego. Dla instrukcji LPM najmłodszy bit rejestru Z wybiera młodszy bajt stałej, jeśli jest wyzerowany, lub starszy bajt stałej, jeśli jest ustawiony na 1.

ATtiny11/12 używa 3-poziomowego stosu sprzętowego dla podprogramów i przerwań. Komórki stosu sprzętowego posiadają

szerokość 9 bitów i przechowują adresy powrotne licznika programu (PC), gdy nastąpiło wywołanie

podprogramu lub procedury obsługi przerwania.

Instrukcje RCALL i przerwania umieszczają adres powrotny dla rejestru PC na poziomie 0 stosu,

a dane znajdujące się na poziomach stosu 1-2 są przesuwane o jeden poziom w głąb stosu. Gdy zostaje wykonana instrukcja RET

lub RETI, adres powrotu jest pobierany do PC z poziomu 0 stosu, a dane z poziomów 1-2 są przesuwane o jeden poziom w górę

stosu.

Jeśli wystąpią kolejno więcej niż 3 wywołania podprogramów lub przerwań, to pierwsze wartości zapisane na stosie ulegną nadpisaniu. Umieszczenie na stosie czterech adresów powrotnych A1, A2, A3 i A4, a następnie wykonanie czterech powrotów, pobierze ze stosu A4, A3, A2 i jeszcze raz A2.

Na pierwszy rzut oka może to wyglądać na wadę mikrokontrolera. Pamiętaj jednak, iż ATtiny11/12 opracowano specjalnie dla prostych zastosowań. Jeśli potrzebujesz wywoływać dużo podprogramów lub stosujesz złożony system przerwań, to prawdopodobnie potrzebny będzie ci inny mikrokontroler.

ATtiny12 zawiera pamięć danych EEPROM (ang. electrically erasable programmable read-only memory) o pojemności 64 bajtów. Została ona zorganizowana jako oddzielna przestrzeń danych, w której można odczytywać i zapisywać pojedyncze bajty. EEPROM ma trwałość co najmniej 100,000 cykli zapisu/kasowania. Dokładny opis sposobu obsługi pamięci EEPROM przez mikroprocesor AVR znajdziesz w rozdziale " Dostęp do pamięci EEPROM w ATtiny12".

Istnieje również możliwość odczytywania/zapisu zawartości EEPROM poprzez interfejs SPI, co opisuje rozdział "Programowanie pamięci".

Ten rozdział opisuje ogólne zagadnienia chronometrażu wykonywania instrukcji. Mikroprocesor AVR jest synchronizowany impulsami zegarowymi clkCPU bezpośrednio generowanymi przez zewnętrzny kwarc. Wewnątrz nie jest stosowany żaden podział zegara.

Powyższy rysunek pokazuje równoległe pobrania i wykonania instrukcji w architekturze harwardzkiej. Jest to podstawowa koncepcja nakładkowania w celu osiągnięcia do 1 MIPS (ang. Million Instructions per Second – milion operacji na sekundę) na 1 MHz z odpowiednimi unikalnymi wynikami zmniejszania kosztów, wykorzystania zegara oraz zmniejszenia poboru energii.

Niżej przedstawiono wewnętrzny chronometraż dostępu do zestawu rejestrów. W pojedynczym cyklu zegara wykonywana jest operacja jednostki arytmetyczno-logicznej przy użyciu dwóch argumentów-rejestrów, a wynik zostaje z powrotem umieszczony w rejestrze docelowym.

Poniższa tabela przedstawia przeznaczenie komórek przestrzeni we/wy w ATtiny11/12:

| Adres | Nazwa | Mikrokontroler | Funkcja |

| 0x3F | SREG | ATtiny11/12 | Rejestr stanu |

| 0x3B | GIMSK | ATtiny11/12 | Ogólny rejestr masek przerwań |

| 0x3A | GIFR | ATtiny11/12 | Ogólny rejestr znaczników przerwań |

| 0x39 | TIMSK | ATtiny11/12 | Rejestr maski przerwań dla timera/licznika |

| 0x38 | TIFR | ATtiny11/12 | Rejestr znaczników przerwań dla timera/licznika |

| 0x35 | MCUCR | ATtiny11/12 | Rejestr sterowania mikrokontrolerem |

| 0x34 | MCUSR | ATtiny11/12 | Rejestr stanu mikrokontrolera |

| 0x33 | TCCR0 | ATtiny11/12 | Rejestr sterowania timerem/licznikiem 0 |

| 0x32 | TCNT0 | ATtiny11/12 | Rejestr zawartości timera/licznika 0 (8-bitów) |

| 0x31 | OSCCAL | ATtiny12 | Rejestr kalibracji oscylatora |

| 0x21 | WDTCR | ATtiny11/12 | Rejestr sterowania licznikiem zegarowym |

| 0x1E | EEAR | ATtiny12 | Rejestr adresowy dla EEPROM |

| 0x1D | EEDR | ATtiny12 | Rejestr danych dla EEPROM |

| 0x1C | EECR | ATtiny12 | Rejestr sterujący EEPROM |

| 0x18 | PORTB | ATtiny11/12 | Rejestr danych portu B |

| 0x17 | DDRB | ATtiny11/12 | Rejestr kierunku danych portu B |

| 0x16 | PINB | ATtiny11/12 | Rejestr odczytu portu B |

| 0x08 | ACSR | ATtiny11/12 | Rejestr sterowania i stanu komparatora analogowego |

Uwaga: W tabeli zostały pominięte komórki zarezerwowane lub nieużywane.

Wszystkie układy peryferyjne ATtiny11/12 I/O są obsługiwane poprzez przestrzeń we/wy. Komórki w tej przestrzeni są odczytywane i zapisywane odpowiednio instrukcjami IN i OUT, które wykonują przesył danych pomiędzy 32 rejestrami ogólnego przeznaczenia a przestrzenią we/wy.. Rejestry we/wy znajdujące się w zakresie adresów od 0x00 do 0x1F są bezpośrednio dostępne bitowo za pomocą instrukcji SBI i CBI. W tych rejestrach wartość pojedynczych bitów można sprawdzać przy użyciu instrukcji SBIS i SBIC.

Dla kompatybilności z przyszłymi modelami mikrokontrolerów zarezerwowane bity powinny przy dostępie być zapisywane wartością 0. Zarezerwowanych adresów pamięci we/wy nigdy nie należy zapisywać.

Rejestr stanu mikroprocesora (SREG) umieszczony w przestrzeni we/wy pod adresem 0x3F posiada następującą definicję:

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x3F | I | T | H | S | V | N | Z | C | SREG |

| Zapis/Odczyt | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit globalnego uaktywnienia przerwań (ang. Global Interrupt Enable bit) musi być ustawiony, aby mikrokontroler zaczął reagować na przerwania. Włączanie indywidualnych przerwań wykonywane jest wtedy w oddzielnych rejestrach sterujących. Jeśli bit ten jest wyzerowany, to żadne przerwanie nie będzie aktywne bez względu na indywidualne ustawienia przerwań. Bit I jest zerowany przez logikę mikrokontrolera po wystąpieniu jakiegoś przerwania, a jest z powrotem ustawiany na 1 przez instrukcję RETI, aby włączyć obsługę kolejnych przerwań. Bit I może również być zerowany i ustawiany przez instrukcje SEI i CLI (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

Instrukcje kopiowania bitu BLD (Bit LoaD) i BST (Bit STore) używają bitu T jako bitu źródłowego i docelowego. Bit z rejestru można skopiować do T za pomocą instrukcji BST, a bit w T można skopiować do bitu w rejestrze za pomocą instrukcji BLD.

Znacznik H oznacza przeniesienie połówkowe (z bitu czwartego na piąty) w niektórych operacjach arytmetycznych. Jest on użyteczny w arytmetyce liczb BCD (ang. binary coded decimal – liczby dziesiętne kodowane dwójkowo) (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

Bit znaku jest zawsze wynikiem operacji sumy modulo dwa pomiędzy znacznikiem liczby ujemnej N oraz znacznikiem nadmiaru V liczb w systemie uzupełnień do podstawy 2 (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

Znacznik ten wspiera arytmetykę liczb w systemie U2 (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

Znacznik ten wskazuje na ujemny wynik w operacji arytmetycznej lub logicznej (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

Znacznik ten oznacza zerowy wynik w operacji arytmetycznej lub logicznej (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

Znacznik C wskazuje na przeniesienie w operacji arytmetycznej lub logicznej (zobacz do rozdziałów "Instrukcje AVR" i "Zestaw instrukcji").

ATtiny11 udostępnia cztery różne źródła przerwań, a ATtiny12 udostępnia ich pięć. Te przerwania oraz resetowanie posiadają swoje oddzielne wektory w pamięci programu. Wszystkie przerwania mają przydzielone indywidualne bity uaktywniające, które muszą być ustawione w stan logiczny jeden wraz z bitem I w rejestrze stanu, aby włączyć obsługę danego przerwania.

Najniższe adresy w pamięci programu są automatycznie zdefiniowane jako wektory resetu oraz przerwań. Kompletną listę wektorów prezentuje tabela poniżej. Lista ta określa również poziomy priorytetów różnych przerwań. Im niższy adres posiada wektor przerwania, tym wyższy priorytet ma to przerwanie. Najwyższy priorytet ma RESET, a następny należy do INT0 – żądania obsługi przerwania zewnętrznego 0, itd.

| Numer wektora |

Model mikrokontrolera |

Adres wektora |

Źródło przerwania |

Opis przerwania |

| 1 | ATtiny11 | 0x000 | RESET |

Końcówka RESET,

resetowanie przy włączeniu zasilania i od licznika zegarowego |

| 1 | ATtiny12 | 0x000 | RESET |

Końcówka RESET,

resetowanie przy włączeniu zasilania, przy spadku napięcia zasilania i od licznika zegarowego |

| 2 | ATtiny11/12 | 0x001 | INT0 | Żądanie

przerwania zewnętrznego 0 |

| 3 | ATtiny11/12 | 0x002 | Końcówki we/wy | Zmiana stanu końcówek we/wy. |

| 4 | ATtiny11/12 | 0x003 | TIMER0, OVF0 | Timer/licznik 0, przepełnienie |

| 5 | ATtiny11 | 0x004 | ANA_COMP | Komparator analogowy |

| 5 | ATtiny12 | 0x004 | EE_RDY | Gotowość pamięci EEPROM |

| 6 | ATtiny12 | 0x005 | ANA_COMP | Komparator analogowy |

Najbardziej typowy i ogólny układ programu dla wektorów RESET i przerwań dla ATtiny11 jest następujący:

Adres Etykiety Kod Komentarze 0x000 rjmp RESET ; Obsługa Reset 0x001 rjmp EXT_INT0 ; Obsługa IRQ0 0x002 rjmp PIN_CHANGE ; Obsługa zmiany stanu końcówki 0x003 rjmp TIM0_OVF ; Obsługa przepełnienia Timera 0 0x004 rjmp ANA_COMP ; Obsługa komparatora analogowego ; 0x005 MAIN: <instr> xxx ; Początek głównego programu ... ... ; ... |

Najbardziej typowy i ogólny układ programu dla wektorów RESET i przerwań dla ATtiny12 jest następujący:

Adres Etykiety Kod Komentarze 0x000 rjmp RESET ; Obsługa Reset 0x001 rjmp EXT_INT0 ; Obsługa IRQ0 0x002 rjmp PIN_CHANGE ; Obsługa zmiany stanu końcówki 0x003 rjmp TIM0_OVF ; Obsługa przepełnienia Timera 0 0x004 rjmp EE_RDY ; Obsługa gotowości EEPROM 0x005 rjmp ANA_COMP ; Obsługa komparatora analogowego ; 0x005 MAIN: <instr> xxx ; Początek głównego programu ... ... ; ... |

ATtiny11/12 dostarcza trzech lub czterech źródeł resetowania:

Podczas resetu wszystkie rejestry we/wy zostają przywrócone do swoich początkowych wartości, a wykonanie programu rozpoczyna się od adresu 0x000. Instrukcją umieszczoną pod tym adresem musi być rozkaz skoku względnego RJMP, która powoduje przejście do procedury obsługi resetowania. Jeśli program nigdy nie uaktywnia żadnego źródła przerwań, to wektory przerwań nie są używane i w ich miejscu może się znaleźć normalny kod programu. Poniższy rysunek pokazuje logikę resetu dla ATtiny11:

Tabela poniżej definiuje parametry elektryczne układów resetu dla ATtiny11.

| Symbol | Parametr | Min. | Typowo | Max. | Jednostka |

| VPOT(1) | Napięcie progowe dla resetu przy włączeniu zasilania (rosnąco) | 1,0 | 1,4 | 1,8 | V |

| Napięcie progowe dla resetu przy włączeniu zasilania (opadajaco) | 0,4 | 0,6 | 0,8 | V | |

| VRST | Napięcie progowe końcówki RESET | 0,6VCC | V |

| Uwaga: | 1. Reset przy włączeniu zasilania (ang. Power-on Reset) nie zadziała, aż napięcie zasilające miało spadek poniżej VPOT (opadająco). |

Układ resetu przy włączaniu zasilania (ang. Power-on Reset circuit) zapewnia resetowanie mikrokontrolera przy włączaniu.

Jak pokazano na rysunku powyżej wewnętrzny timer jest taktowany z oscylatora RC licznika zegarowego. Timer ten zapobiega uruchomieniu mikrokontrolera przez pewien czas po osiągnięciu przez napięcie zasilające napięcia progu załączania VPOT (ang. Power-on Threshold Voltage).

Całkowity okres resetu jest równy czasowi opóźnienia – tTOUT. Bit bezpiecznikowy FSTRT w pamięci FLASH można zaprogramować w celu skrócenia czasu uruchamiania. Poniższa tablica pokazuje czasy uruchamiania dla różnych opcji zegara. Oscylator licznika zegarowego jest używany do odmierzania czasu uruchamiania, a ten oscylator jest zależny od napięcia, co opisane zostało w podrozdziale “Typowe Parametry ATtiny11".

| Wybrana opcja zegara | Czas uruchamiania tTOUT | |

| FSTR niezaprogramowany |

FSTRT zaprogramowany |

|

| Zewnętrzny kwarc | 67 ms | 4,2 ms |

| Zewnętrzny rezonator ceramiczny | 67 ms | 4,2 ms |

| Zewnętrzny kwarc o niskiej częstotliwości | 4,2 s | 4,2 s |

| Zewnętrzny oscylator RC | 4,2 ms | 67 μs |

| Wewnętrzny oscylator RC | 4,2 ms | 67 μs |

| Zewnętrzny zegar | 4,2 ms | 5 cykli od

resetu, 2 cykle od wyłączenia |

Jeśli wewnętrzne opóźnienie uruchamiania jest wystarczające, to końcówka RESET może być połączona bezpośrednio z VCC lub poprzez zewnętrzny opornik podciągający. Utrzymanie końcówki RESET w stanie niskim przez pewien okres po włączeniu napięcia zasilającego VCC powoduje wydłużenie okresu resetu przy włączeniu zasilania:

Logika resetu dla ATtiny12 wygląda następująco:

| Symbol | Parametr | Warunek | Min. | Typowo | Max. | Jednostka |

| VPOT(1) | Napięcie progowe dla resetu przy włączeniu zasilania (rosnąco) | BOD(2) wyłączone | 1,0 | 1,4 | 1,8 | V |

| BOD włączone | 0,6 | 1,2 | 1,8 | V | ||

| Napięcie progowe dla resetu przy włączeniu zasilania (opadająco) | BOD wyłączone | 0,4 | 0,6 | 0,8 | V | |

| BOD włączone | 0,6 | 1,2 | 1,8 | V | ||

| VRST | Napięcie progowe końcówki RESET | 0,6VCC | V | |||

| VBOT | Napięcie progowe dla spadku napięcia zasilania | (BODLEVEL = 1) | 1,5 | 1,8 | 1,9 | V |

| (BODLEVEL = 0) | 2,3 | 2,7 | 2,8 | V |

| CKSEL3..0 | Źródło zegarowe | Czas uruchamiania VCC = 1,8V BODLEVEL niezaprogramowane |

Czas uruchamiania VCC = 2,7V BODLEVEL zaprogramowane |

| 1111 | Zewnętrzny kwarc/rezonator ceramiczny(1) | 1K CK | 1K CK |

| 1110 | Zewnętrzny kwarc/rezonator ceramiczny(1) | 3,6 ms + 1K CK | 4,2 ms + 1K CK |

| 1101 | Zewnętrzny kwarc/rezonator ceramiczny(1) | 57 ms + 1K CK | 67 ms + 1K CK |

| 1100 | Zewnętrzny kwarc/rezonator ceramiczny | 16K CK | 16K CK |

| 1011 | Zewnętrzny kwarc/rezonator ceramiczny | 3,6 ms + 16K CK | 4,2 ms + 16K CK |

| 1010 | Zewnętrzny kwarc/rezonator ceramiczny | 57 ms + 16 CK | 67 ms + 16K CK |

| 1001 | Kwarc o niskiej częstotliwości | 57 ms + 1K CK | 67 ms + 16K CK |

| 1000 | Kwarc o niskiej częstotliwości | 57 ms + 32K CK | 67 ms + 16K CK |

| 0111 | Zewnętrzny oscylator RC | 6 CK | 6CK |

| 0110 | Zewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0101 | Zewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0100 | Wewnętrzny oscylator RC | 6 CK | 6CK |

| 0011 | Wewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0010 | Wewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0001 | Zewnętrzny zegar | 6 CK | 6CK |

| 0000 | Zewnętrzny zegar | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| Uwaga: | 1. | Z powodu ograniczonej liczby cykli zegarowych w okresie uruchamiania zaleca się korzystanie z rezonatora ceramicznego. |

Powyższa tabela pokazuje czasy uruchamiania od momentu resetu. Przy wybudzaniu używana jest tylko część czasu uruchamiania związana z zegarem CK. Do odmierzania okresu przy uruchamianiu wykorzystuje się oscylator licznika zegarowego. Liczba cykli tego oscylatora pokazana jest w poniżej tabeli.

| BODLEVEL | Okres | Liczba cykli |

| Niezaprogramowany | 3,6 ms (przy VCC = 1,8V) | 256 |

| Niezaprogramowany | 57 ms (przy VCC = 1,8V) | 4K |

| Zaprogramowany | 4,2 ms (przy VCC = 2,7V) | 1K |

| Zaprogramowany | 67 ms (przy VCC = 2,7V) | 16K |

Częstotliwość oscylatora licznika zegarowego zależy od napięcia, co opisano dokładnie w podrozdziale "Typowe Parametry ATtiny11".

Zwróć uwagę, iż bit bezpiecznikowy BODLEVEL może zostać użyty do wyboru czasów uruchamiania, nawet jeśli wykrywanie spadku napięcia zasilania (ang. Brownout Detection) jest wyłączone (przez pozostawienie bitu bezpiecznikowego BODEN w stanie niezaprogramowanym).

Mikrokontroler jest produkowany z ustawieniem CKSEL3..0 = 0010 (wewnętrzny oscylator RC).

Impuls resetu przy włączaniu zasilania (ang. Power-on Reset, POR) jest generowany przez wewnętrzny obwód wykrywania. Poziom wykrywania wynosi nominalnie 1.4V. POR jest aktywowany zawsze, gdy napięcie zasilania VCC spadnie poniżej poziomu wykrywania. Obwód POR może być użyty do wyzwolenia resetu przy uruchamianiu (ang. the start-up reset) jak również do wykrywania awarii napięcia zasilającego.

Obwód POR zapewnia resetowanie mikrokontrolera przy włączeniu zasilania. Gdy zostanie osiągnięte napięcie progowe resetu przy włączaniu, to uruchamiany jest licznik opóźniający, który określa opóźnienie, w ciągu którego mikrokontroler jest utrzymywany w stanie resetu po wzroście VCC. Okres przewinięcia się licznika opóźniającego może zostać zdefiniowany przez użytkownika poprzez bity bezpiecznikowe CKSEL. Ustawienia tych bitów i związane z nimi czasy opóźnień pokazuje poniższa tabela:

| CKSEL3..0 | Źródło zegarowe | Czas uruchamiania VCC = 1,8V BODLEVEL niezaprogramowane |

Czas uruchamiania VCC = 2,7V BODLEVEL zaprogramowane |

| 1111 | Zewnętrzny kwarc/rezonator ceramiczny(1) | 1K CK | 1K CK |

| 1110 | Zewnętrzny kwarc/rezonator ceramiczny(1) | 3,6 ms + 1K CK | 4,2 ms + 1K CK |

| 1101 | Zewnętrzny kwarc/rezonator ceramiczny(1) | 57 ms + 1K CK | 67 ms + 1K CK |

| 1100 | Zewnętrzny kwarc/rezonator ceramiczny | 16K CK | 16K CK |

| 1011 | Zewnętrzny kwarc/rezonator ceramiczny | 3,6 ms + 16K CK | 4,2 ms + 16K CK |

| 1010 | Zewnętrzny kwarc/rezonator ceramiczny | 57 ms + 16 CK | 67 ms + 16K CK |

| 1001 | Kwarc o niskiej częstotliwości | 57 ms + 1K CK | 67 ms + 16K CK |

| 1000 | Kwarc o niskiej częstotliwości | 57 ms + 32K CK | 67 ms + 16K CK |

| 0111 | Zewnętrzny oscylator RC | 6 CK | 6 CK |

| 0110 | Zewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0101 | Zewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0100 | Wewnętrzny oscylator RC | 6 CK | 6 CK |

| 0011 | Wewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0010 | Wewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0001 | Zewnętrzny zegar | 6 CK | 6 CK |

| 0000 | Zewnętrzny zegar | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| Uwaga: | 1. | Z powodu ograniczonej liczby cykli zegarowych w okresie uruchamiania zaleca się korzystanie z rezonatora ceramicznego. |

Sygnał resetu jest aktywowany ponownie bez żadnego opóźnienia, gdy VCC spada poniżej poziomu wykrywania. Jeśli wewnętrzne opóźnienie uruchamiania jest wystarczające, to końcówka RESET może być połączona bezpośrednio z VCC lub poprzez zewnętrzny opornik podciągający. Utrzymanie końcówki RESET w stanie niskim przez pewien okres po włączeniu napięcia zasilającego VCC powoduje wydłużenie okresu resetu przy włączeniu zasilania:

Zewnętrzne resetowanie generowane jest przez niski stan na końcówce RESET. Impuls resetu dłuższy niż 50 ns wygeneruje reset, nawet jeśli zegar mikrokontrolera nie pracuje. Krótsze impulsy nie dają gwarancji wygenerowania resetu. Gdy zastosowany sygnał osiągnie napięcie progu resetowania VRST (ang. Reset Threshold Voltage) na krawędzi dodatniej (narastającej, 0 → 1), licznik opóźnienia uruchomi mikrokontroler po upływie okresu opóźnienia tTOUT.

ATtiny12 posiada wbudowany obwód wykrywania spadku napięcia zasilającego (ang. brown-out detection circuit, BOD) do monitorowania poziomu Vcc podczas pracy. Obwód BOD może zostać włączony/wyłączony za pomocą bitu bezpiecznikowego BODEN. Gdy BODEN jest włączone (bit BODEN zaprogramowany), a napięcie Vcc spadnie poniżej poziomu wyzwalania, to zostaje natychmiast aktywowany reset przy spadku napięcia zasilania (ang. brown-out reset). Gdy Vcc wzrośnie powyżej poziomu wyzwalania, reset od spadku napięcia zasilania zostaje dezaktywowany po pewnym opóźnieniu, które definiuje użytkownik w ten sam sposób, co opóźnienie sygnału POR. Poziom wyzwalania dla BOD można wybrać bitem bezpiecznikowym BODLEVEL na 1,8V (BODLEVEL niezaprogramowany) lub 2,7V (BODLEVEL zaprogramowany). Poziom wyzwalania ma histerezę 50mV w celu ochrony przed wykryciem szpilkowych spadków napięcia..

Obwód BOD tylko wtedy wykryje spadek Vcc, jeśli to napięcie utrzyma się poniżej progu wyzwalania dłużej niż 7 μs dla poziomu wyzwalania 2,7V, 3 μs dla poziomu wyzwalania 1,8V (wartości typowe).

| Uwaga: | Histereza dla VBOT: VBOT+ = VBOT + 25 mV VBOT– = VBOT – 25 mV. |

Gdy licznik zegarowy dojdzie do końca okresu swojego zliczania, wygeneruje krótki impuls reset o czasie trwania równym jednemu cyklowi zegara CK. Przy opadającym zboczu tego impulsu licznik opóźnienia zaczyna zliczać okres opóźnienia tTOUT.

Rejestr stanu mikrokontrolera udostępnia informację o źródle zresetowania mikrokontrolera.

Te bity są zarezerwowane w ATtiny11 i zawsze dają odczyt zero.

Po resecie przy włączeniu zasilania (ang. power-on reset) ten bit ma niezdefiniowany stan (X). Zostanie on ustawiony przez reset zewnętrzny. Reset od licznika zegarowego pozostawia ten bit w stanie niezmienionym.

Ten bit jest ustawiany przez reset przy włączaniu zasilania. Reset od licznika zegarowego lub reset zewnętrzny pozostawiają ten biit bez zmian.

Dla podsumowania poniższa tabela pokazuje wartości tych dwóch bitów po trzech trybach resetu:

| Źródło resetu | EXTRF | PORF |

| Włączenie zasilania | niezdefiniowany | 1 |

| Zewnętrzny reset | 1 | niezmieniany |

| Reset od licznika zegarowego | niezmieniany | niezmieniany |

Aby zidentyfikować warunek resetu, oprogramowanie użytkownika powinno wyzerować oba bity PORF i EXTRF najwcześniej, jak to możliwe w programie. Sprawdzanie wartości PORF i EXTRF jest wykonywane przed wyzerowaniem bitów. Jeśli dany bit zostanie wyzerowany przed wystąpieniem resetu zewnętrznego lub resetu od licznika zegarowego, to źródło resetu można znaleźć wykorzystując poniższą tabelę prawdy:

| EXTRF | PORF | Źródło resetu |

| 0 | 0 | Licznik zegarowy |

| 1 | 0 | Reset zewnętrzny |

| 0 | 1 | Reset przy włączaniu zasilania |

| 1 | 1 | Reset przy włączaniu zasilania |

Rejestr stanu mikrokontrolera udostępnia informację o źródle zresetowania mikrokontrolera.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x34 | - | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Zapis/Odczyt | O | O | O | O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | Zobacz na opis bitów | ||||

Te bity są zarezerwowane w ATtiny12 i zawsze dają odczyt zero.

Ten bit zostaje ustawiony, gdy występuje reset spowodowany przepełnieniem licznika zegarowego. Bit jest zerowany przez reset przy włączeniu zasilania lub przez zapis logicznego zera do tego znacznika.

Ten bit jest ustawiany, jeśli wystąpi reset przy spadku napięcia zasilania. Bit jest zerowany przez reset przy włączeniu zasilania lub przez zapis logicznego zera do tego znacznika.

Ten bit jest ustawiany, jeśli wystąpi reset zewnętrzny. Bit jest zerowany przez reset przy włączeniu zasilania lub przez zapis logicznego zera do tego znacznika.

Ten bit zostaje ustawiony, jeśli wystąpi reset przy włączeniu zasilania. Bit jest resetowany przez zapis logicznego zera do tego znacznika.

Aby wykorzystać znaczniki resetu do identyfikacji warunku resetu, użytkownik powinien odczytać, a następnie wyzerować rejestr MCUSR najwcześniej jak tylko to możliwe w programie. Jeśli rejestr został wyzerowany przed wystąpieniem kolejnego resetu, to źródło resetu można znaleźć przez zbadanie znaczników resetu.

ATtiny12 posiada możliwość stosowania wewnętrznego napięcia odniesienia o nominalnej wartości 1,22V. Napięcie to jest używane przy wykrywaniu spadków napięcia zasilającego (ang. Brown-out Detection) i można je wykorzystać jako napięcie wejściowe dla komparatora analogowego.

Napięcie odniesienia posiada pewien czas uruchamiania się, który może wpłynąć na sposób używania tego napięcia. Maksymalny czas uruchamiania wynosi 10μs. Aby zaoszczędzić energię, odniesienie to nie zawsze jest włączone. Jest ono włączane w następujących sytuacjach:

W ten sposób, gdy BOD (ang. Brown-out Detection, wykrywanie spadku napięcia zasilającego) nie jest włączone, po ustawieniu bitu AINBG użytkownik zawsze musi odczekać, aż odniesienie się w pełni uruchomi, zanim będzie można je wykorzystywać z wyjściem komparatora analogowego. Obwód napięcia odniesienia pobiera w przybliżeniu prąd 10 μA, a w celu zmniejszenia poboru energii w trybie wyłączenia zasilania (ang. Power-down mode) użytkownik może wyłączyć odniesienie przed wejściem w ten tryb.

ATtiny11/12 posiada dwa 8-bitowe rejestry maskowania przerwań: GIMSK – ogólny rejestr maskowania przerwań (ang. General Interrupt Mask Register) i TIMSK – rejestr maskowania przerwań od timera/licznika (ang. Timer/Counter Interrupt Mask Register).

Gdy wystąpi przerwanie, zerowany jest bit I globalnego uaktywnienia przerwań (ang. Global Interrupt Enable I-bit) w rejestrze stanu i wszystkie przerwania zostają zablokowane. Oprogramowanie użytkownika może ustawić z powrotem bit I, aby włączyć przerwania zagnieżdżone. Bit I jest ustawiany, gdy jest wykonywana instrukcja powrotu z przerwania – RETI.

Gdy licznik programu (ang. Program Counter, PC) jest ustawiany na adres wektora w celu wykonania procedury obsługi przerwania, odpowiedni znacznik przerwania zostaje sprzętowo wyzerowany. Niektóre znaczniki przerwań można również wyzerować przez zapis logicznej jedynki na pozycji bitu znacznika do wyzerowania.

Jeśli warunek przerwania wystąpi, gdy odpowiadający mu bit uaktywnienia jest wyzerowany, to znacznik przerwania zostanie ustawiony i zapamiętany aż do uaktywnienia przerwania lub do wyzerowania tego znacznika przez oprogramowanie.

Gdy wystąpi jeden lub więcej warunków przerwania, gdy bit I globalnego uaktywnienia przerwań jest wyzerowany, to odpowiednie znaczniki przerwań zostaną ustawione i zapamiętane, aż do ustawienia bitu I, a następnie zostaną wykonane w kolejności ich priorytetów.

Zwróć uwagę, iż przerwanie od zewnętrznego poziomu nie posiada znacznika i będzie pamiętane tak długo, jak długo aktywny jest warunek przerwania.

Również zauważ, iż rejestr stanu nie jest automatycznie zapamiętywany przy wejściu do procedury obsługującej przerwanie, ani nie zostaje automatycznie odtworzony przy powrocie z tej procedury. Operacje te muszą zostać wykonane programowo.

Czas reakcji na przerwanie dla wszystkich uaktywnionych przerwań AVR wynosi co najmniej 4 cykle zegarowe. Po tym okresie 4 cykli zegarowych licznik programu (9 bitów) jest umieszczany na stosie, po czym wykonany zostaje rozkaz umieszczony w wektorze przerwania, będący najczęściej skokiem względnym RJMP do procedury obsługi przerwania, a skok ten zajmuje dodatkowe dwa cykle zegarowe. Jeśli przerwanie wystąpi podczas instrukcji wielocyklowej, to wykonanie tej instrukcji zostaje doprowadzone do końca przed obsłużeniem przerwania. W ATtiny12, jeśli przerwanie wystąpi w trakcie uśpienia mikrokontrolera, to czas reakcji wydłuża się o 4 dalsze cykle zegarowe.

Powrót z procedury przerwania zajmuje 4 cykle zegarowe, podczas których licznik programu (9 bitów) jest pobierany z powrotem ze stosu, a znacznik I w SREG jest ustawiany. Gdy mikrokontroler AVR wychodzi z przerwania, zawsze powraca do programu, który był wykonywany w momencie wystąpienia przerwania i wykonuje jedną dalszą instrukcję, zanim zostanie obsłużone jakiekolwiek oczekujące przerwanie.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x3B | - | INT0 | PCIE | - | - | - | - | - | GIMSK |

| Zapis/Odczyt | O | Z/O | Z/O | O | O | O | O | O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Te bity są zarezerwowane w ATtiny11/12 i przy odczycie zawsze dają wartość 0.

Gdy bit INT0 zostanie ustawiony i bit I w rejestrze stanu (SREG) jest również ustawiony, to zostanie uaktywnione przerwanie zewnętrzne z końcówki INT0 (nóżka nr 6). Bity 1:0 sterujące sposobem wykrywania przerwania 0 (ang. Interrupt Sense Control0 bits) (ISC01 i ISC00) w ogólnym rejestrze sterującym mikrokontrolera (ang. MCU general Control Register) (MCUCR) definiują, czy przerwanie zewnętrzne będzie aktywowane narastającym/opadającym zboczem sygnału, zmianą stanu końcówki, czy niskim poziomem na końcówce INT0. Aktywność na tej końcówce spowoduje żądanie przerwania nawet, jeśli końcówka INT0 jest skonfigurowana jako wyjście. Procedura obsługi żądania przerwania 0 rozpoczyna się od adresu 0x001.

Gdy bit PCIE zostanie ustawiony i bit I w rejestrze stanu (SREG) jest ustawiony, to zostanie uaktywnione przerwanie przy zmianie stanu końcówki. Jakakolwiek zmiana na końcówkach wejściowych lub końcówkach we/wy spowoduje żądanie przerwania. Procedura obsługi tego przerwania rozpoczyna się od adresu 0x002 w pamięci programu.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x3A | - | INTF0 | PCIF | - | - | - | - | - | GIFR |

| Zapis/Odczyt | O | Z/O | Z/O | O | O | O | O | O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Te bity są zarezerwowane w ATtiny11/12 i przy odczycie zawsze dają wartość 0.

Gdy zbocze sygnału na końcówce INT0 (nóżka nr 6) wyzwoli żądanie przerwania, to odpowiadający mu znacznik przerwania INTF0 otrzymuje stan wysoki 1. Jeśli bit I w SREG oraz odpowiedni bit uaktywniający INT0 w rejestrze GIMSK są ustawione, to mikrokontroler wykona skok do wektora przerwania. Znacznik ten zostaje wyzerowany, gdy rozpocznie się wykonywanie procedury przerwania. Alternatywnie znacznik można wyzerować przez zapis w nim stanu 1. Znacznik ten jest zawsze wyzerowany, gdy końcówka INT0 zostanie skonfigurowana na przerwanie od poziomu niskiego.

Gdy pewne zdarzenie na dowolnej końcówce wejścia lub końcówce we/wy wyzwoli żądanie przerwania, to bit PCIF jest ustawiany na 1. Jeśli bit I w SREG i bit PCIE w GIMSK są ustawione, to mikrokontroler skoczy do wektora przerwania pod adresem 0x002. Znacznik zostaje wyzerowany, gdy procedura obsługi przerwania zacznie być wykonywana. Alternatywnie znacznik można wyzerować przez zapis do niego logicznej jedynki.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x39 | - | - | - | - | - | - | TOIE0 | - | TIMSK |

| Zapis/Odczyt | O | O | O | O | O | O | Z/O | O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Te bity są zarezerwowane w ATtiny11/12 i przy odczycie zawsze dają wartość 0.

Gdy bit TOIE0 zostanie ustawiony i bit I w rejestrze stanu (SREG) jest ustawiony, to zostanie uaktywnione przerwanie od przepełnienia timera/licznika 0. Odpowiedni wektor przerwania (pod adresem 0x003) jest wykonywany, gdy wystąpi przepełnienie w timerze/liczniku 0, tj. gdy zostanie ustawiony znacznik przepełnienia w rejestrze znacznika przerwania od timera/licznika 0 – TIFR.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x38 | - | - | - | - | - | - | TOV0 | - | TIFR |

| Zapis/Odczyt | O | O | O | O | O | O | Z/O | O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Te bity są zarezerwowane w ATtiny11/12 i przy odczycie zawsze dają wartość 0.

Bit TOV0 jest ustawiany, gdy wystąpi przepełnienie w timerze/liczniku 0. TOV0 jest zerowany sprzętowo przy wykonywaniu odpowiedniego wektora obsługi przerwania. Alternatywnie TOV0 można wyzerować przez zapis logicznej jedynki na pozycji jego bitu. Gdy są ustawione bity: I w SREG, TOIE0 (Timer/Counter0 Overf low Interrupt Enable – uaktywnienie przerwań przy przepełnieniu timera/licznika 0) w TIMSK, i TOV0, to zostaje wykonane przerwanie przy przepełnieniu timera/licznika 0.

Przerwanie zewnętrzne (ang. External Interrupt) jest wyzwalane przez końcówkę INT0 (nóżka nr 6). Zwróć uwagę, iż jeśli przerwanie to jest uaktywnione, to zostanie wyzwolone nawet wtedy, gdy końcówka INT0 pracuje jako wyjście. Ta cecha dostarcza sposobu generowania przerwań programowych. Przerwanie zewnętrzne może zostać wyzwolone przez opadające/narastające zbocze, zmianę stanu końcówki lub niski poziom logiczny 0. Ustawia się to w rejestrze sterowania mikrokontrolerem (ang. MCU Control Register – MCUCR). Gdy przerwanie zewnętrzne zostało uaktywnione i skonfigurowane na wyzwalanie poziomem, przerwanie będzie wyzwalane tak długo, jak jego końcówka utrzymywana jest w stanie niskim 0.

Przerwanie przy zmianie stanu końcówki (ang. Pin Change Interrupt) jest wyzwalane przez każdą zmianę na dowolnej końcówce wejścia lub we/wy. Zmiana na końcówkach PB2:0 zawsze wywoła przerwanie. Zmiana na końcówkach PB5:3 wywoła przerwanie, jeśli końcówka pracuje jako wejście lub we/wy. Zauważ, iż, jeśli przerwanie zostało aktywowane to zostanie wyzwolone nawet wtedy, gdy końcówka pracuje jako wyjście. Ta cecha pozwala generować przerwania programowe. Zauważ również, iż przerwanie od zmiany stanu końcówki zostanie wyzwolone, nawet jeśli aktywność na danej końcówce wyzwala inne przerwanie, np. przerwanie zewnętrzne. Wynika z tego, iż jedno zdarzenie zewnętrzne może spowodować kilka przerwań.

Wartości na końcówkach są próbkowane przed wykrywaniem zboczy. Jeśli przerwanie od zmiany stanu końcówki jest aktywne, to impulsy o czasie trwania dłuższym od okresu zegarowego mikroprocesora wygenerują przerwanie. Krótsze impulsy nie dają pewności wygenerowania przerwania.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x35 | - | (PUD) | SE | SM | - | - | ISC01 | ISC00 | MCUCR |

| Zapis/Odczyt | O | Z/O | Z/O | Z/O | O | O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Te bity są zarezerwowane w ATtiny11/12 i przy odczycie zawsze dają wartość 0.

Ten bit jest zarezerwowane w ATtiny11 i przy odczycie zawsze daje wartość 0.

Ustawienie tego bitu wyłącza wszystkie oporniki podciągające portu B. Gdy bit jest wyzerowany, oporniki podciągające mogą być włączane indywidualnie dla poszczególnych linii portu B.

Bit SE musi być ustawiony na 1, aby mikrokontroler wszedł w tryb uśpienia przy wykonywaniu instrukcji SLEEP. Aby uniemożliwić mikrokontrolerowi przypadkowe wejście w tryb uśpienia, o ile nie życzy sobie tego programista, zaleca się ustawianie tego bitu tuż przed wykonaniem instrukcji SLEEP.

Ten bit wybiera pomiędzy dwoma dostępnymi trybami uśpienia. Gdy bit SM jest wyzerowany, zostaje wybrany tryb bezczynny (ang. Idle Mode). Gdy bit SM jest ustawiony, zostaje wybrany tryb wyłączenia zasilania(ang. Power-down Mode). Szczegóły znajdziesz poniżej.

Przerwanie zewnętrzne 0 jest generowane końcówkę INT0, jeśli są ustawione znacznik I w rejestrze stanu SREG oraz odpowiednia maska przerwań. Poniższa tablica pokazuje sposób ustawienia tych bitów dla różnych parametrów przerwania zewnętrznego:

| ISC01 | ISC00 | Opis |

| 0 | 0 | Niski poziom na końcówce INT0 generuje przerwanie |

| 0 | 1 | Dowolna zmiana stanu końcówki INT0 generuje przerwanie |

| 1 | 0 | Opadające zbocze sygnału na końcówce INT0 generuje przerwanie |

| 1 | 1 | Narastające zbocze sygnału na końcówce INT0 generuje przerwanie |

Wartość na końcówce INT0 jest próbkowana przed wykrywaniem zboczy. Jeśli zostało wybrane przerwanie wyzwalane zboczem, to impulsy trwające dłużej od okresu zegarowego mikroprocesora wygenerują przerwanie. Krótsze impulsy nie dają gwarancji wygenerowania przerwania. Jeśli wybrano przerwanie od niskiego poziomu, to niski poziom musi być utrzymywany aż do zakończenia bieżąco wykonywanej instrukcji, aby przerwanie zostało wygenerowane. Jeśli to przerwanie jest uaktywnione, to przerwanie wyzwalane poziomem będzie generowało żądanie przerwania tak długo, jak końcówka ma niski poziom 0.

Aby wejść w tryby uśpienia, musi być ustawiony bit SE w rejestrze sterującym mikrokontrolerem MCUCR oraz musi zostać wykonana instrukcja SLEEP. Bit SM w rejestrze MCUCR wybiera rodzaj trybu uśpienia (bezczynny – Idle lub wyłączenie zasilania – Power-down), który zostanie aktywowany przez instrukcję SLEEP. Jeśli uaktywnione przerwanie wystąpi podczas stanu uśpienia mikrokontrolera, to mikrokontroler wychodzi z uśpienia, wykonuje procedurę przerwania, po czym wznawia wykonywanie programu od kolejnej instrukcji za SLEEP. W czasie wybudzania z trybu wyłączenia zasilania z powodu zmiany stanu końcówki dwa cykle instrukcji są wykonywane zanim znacznik przerwania od zmiany stanu końcówki zostanie uaktualniony. W czasie tych cykli procesor wykonuje instrukcje, lecz warunek przerwania nie jest czytelny, a procedura obsługi przerwania nie została jeszcze uruchomiona. Zawartość zestawu rejestrów oraz pamięci we/wy nie jest zmieniana. Jeśli w trybie uśpienia wystąpi reset, mikrokontroler wybudza się i rozpoczyna wykonywanie programu od wektora Resetu.

Gdy bit SM jest wyzerowany, instrukcja SLEEP wprowadza mikrokontroler w tryb bezczynny (ang. Idle Mode), zatrzymując mikroprocesor, lecz pozostawiając czynne timer/licznik, licznik zegarowy oraz system przerwań. Pozwala to mikrokontrolerowi wybudzić się przy zewnętrznie wyzwalanych przerwaniach jak również przy wewnętrznie wyzwalanych, takich jak przerwanie przy przepełnieniu timera (ang. Timer Overflow Interrupt) i reset od licznika zegarowego (ang. Watchdog Reset). Jeśli wybudzenie od komparatora analogowego nie jest potrzebne, komparator analogowy można wyłączyć przez ustawienie bitu ACD w rejestrze sterowania i stanu komparatora analogowego (ang. Analog Comparator Control and Status Register – ACSR). To zmniejszy pobór prądu w trybie bezczynności. Gdy mikrokontroler wybudza się z trybu bezczynności, mikroprocesor natychmiast podejmuje wykonywanie programu.

Gdy bit SM jest ustawiony, instrukcja SLEEP wprowadza mikrokontroler w tryb wyłączenia zasilania (ang. Powerdown Mode). W tym trybie zewnętrzny oscylator jest zatrzymywany, natomiast przerwania zewnętrzne oraz licznik zegarowy (jeśli uaktywniony) działają. Mikrokontroler może zostać wybudzony tylko przez zewnętrzny reset, przez reset od licznika zegarowego (jeśli uaktywniony), przez zewnętrzne przerwanie niskim poziomem na końcówce INT0 lub przez przerwanie od zmiany poziomu końcówki.

Zauważ, że jeśli wybrano na wybudzanie z trybu wyłączenia zasilania przerwanie wyzwalane niskim poziomem lub zmianą stanu końcówki, to zmieniony poziom musi się utrzymywać przez czas dłuższy od okresu opóźnienia resetu tTOUT. W przeciwnym razie wybudzenie mikrokontrolera nie powiedzie się.

Aby wejść w tryby uśpienia, bit SE w MCUCR musi być ustawiony oraz musi zostać wykonana instrukcja SLEEP. Bit SM w MCUCR wybiera rodzaj trybu uśpienia (bezczynny – Idle lub wyłączenie zasilania – Power-down) do aktywacji przez instrukcję SLEEP. Jeśli w trakcie uśpienia wystąpi aktywowane wcześniej przerwanie, to mikrokontroler wybudza się. Następnie mikroprocesor jest wstrzymywany przez cztery cykle, po czym wykonuje procedurę przerwania i wznawia wykonywanie programu od następnej instrukcji za SLEEP. Zawartość zestawu rejestrów oraz pamięci we/wy nie jest zmieniana. Jeśli w trybie uśpienia wystąpi reset, mikrokontroler wybudza się i rozpoczyna wykonywanie programu od wektora Resetu.

Gdy bit SM jest wyzerowany, instrukcja SLEEP wprowadza mikrokontroler w tryb bezczynny (ang. Idle Mode), zatrzymując mikroprocesor, lecz pozostawiając czynne timer/licznik, licznik zegarowy oraz system przerwań. Pozwala to mikrokontrolerowi wybudzić się przy zewnętrznie wyzwalanych przerwaniach jak również przy wewnętrznie wyzwalanych, takich jak przerwanie przy przepełnieniu timera (ang. Timer Overflow Interrupt) i reset od licznika zegarowego (ang. Watchdog Reset). Jeśli wybudzenie od komparatora analogowego nie jest potrzebne, komparator analogowy można wyłączyć przez ustawienie bitu ACD w rejestrze sterowania i stanu komparatora analogowego (ang. Analog Comparator Control and Status Register – ACSR). To zmniejszy pobór prądu w trybie bezczynności.

Gdy bit SM jest ustawiony, instrukcja SLEEP wprowadza mikrokontroler w tryb wyłączenia zasilania (ang. Powerdown Mode). W tym trybie zewnętrzny oscylator jest zatrzymywany, natomiast przerwania zewnętrzne oraz licznik zegarowy (jeśli uaktywniony) działają. Mikrokontroler może zostać wybudzony tylko przez zewnętrzny reset, przez reset od licznika zegarowego (jeśli uaktywniony), przez zewnętrzne przerwanie niskim poziomem na końcówce INT0 lub przez przerwanie od zmiany poziomu końcówki.

Zauważ, że jeśli do wybudzenia z trybu wyłączenia zasilania używane jest przerwanie od poziomu lub od zmiany stanu końcówki, to zmieniony poziom musi się utrzymywać przez pewien czas, aby wybudzić mikrokontroler. W ten sposób mikrokontroler jest mniej czuły na krótkotrwałe zakłócenia. Okres wybudzenia jest równy części okresu resetu związanej z cyklami zegarowymi CK, jak w poniższej tabeli:

| CKSEL3..0 | Źródło zegarowe | Czas wybudzania VCC = 1,8V BODLEVEL niezaprogramowane |

Czas wybudzania VCC = 2,7V BODLEVEL zaprogramowane |

| 1111 | Zewnętrzny kwarc/rezonator ceramiczny | 1K CK | 1K CK |

| 1110 | Zewnętrzny kwarc/rezonator ceramiczny | 1K CK | 1K CK |

| 1101 | Zewnętrzny kwarc/rezonator ceramiczny | 1K CK | 1K CK |

| 1100 | Zewnętrzny kwarc/rezonator ceramiczny | 16K CK | 16K CK |

| 1011 | Zewnętrzny kwarc/rezonator ceramiczny | 16K CK | 16K CK |

| 1010 | Zewnętrzny kwarc/rezonator ceramiczny | 16 CK | 16K CK |

| 1001 | Kwarc o niskiej częstotliwości | 1K CK | 16K CK |

| 1000 | Kwarc o niskiej częstotliwości | 32K CK | 16K CK |

| 0111 | Zewnętrzny oscylator RC | 6 CK | 6 CK |

| 0110 | Zewnętrzny oscylator RC | 6 CK | 6K CK |

| 0101 | Zewnętrzny oscylator RC | 6 CK | 6K CK |

| 0100 | Wewnętrzny oscylator RC | 6 CK | 6 CK |

| 0011 | Wewnętrzny oscylator RC | 6 CK | 6K CK |

| 0010 | Wewnętrzny oscylator RC | 6 CK | 6K CK |

| 0001 | Zewnętrzny zegar | 6 CK | 6 CK |

| 0000 | Zewnętrzny zegar | 6 CK | 6K CK |

Mikrokontroler wybudzi się z trybu wyłączenia zasilania, jeśli wejście utrzymuje pożądany poziom przez dwa cykle oscylatora licznika zegarowego. Jeśli czas wybudzania jest krótszy od dwóch cykli oscylatora licznika zegarowego, to mikrokontroler wybudzi się, jeśli wejście posiada pożądany poziom przez czas trwania okresu wybudzania. Jeśli warunek wybudzenia zniknie przed upływem okresu wybudzania, to mikrokontroler wybudzi się z trybu wyłączenia zasilania bez obsługi przerwania, które go wybudziło. Okres oscylatora licznika zegarowego jest równy 2,7 μs (nominalnie) przy 3,0V i 25°C. Częstotliwość oscylatora licznika zegarowego jest zależna od napięcia zasilającego, więcej na ten temat znajdziesz w rozdziale "Parametry elektryczne".

Przy wybudzaniu z trybu wyłączonego zasilania występuje pewne opóźnienie od czasu pojawienia się warunku wybudzenia do momentu, gdy ten warunek staje się efektywny. Pozwala to uruchomić zegar i ustabilizować go po tym, jak został zatrzymany. Okres wybudzania jest definiowany przez te same bity bezpiecznikowe CKSEL, które definiują okres opóźnienia resetu (tabela powyżej).

W mikrokontrolerze ATtiny12 kalibrowany oscylator wewnętrzny dostarcza sygnału zegarowego o stałej częstotliwości 1,2 MHz (nominalnie) przy napięciu zasilania 5V i w temperaturze 25°C. Ten zegar może być używany jako zegar systemowy. W podrozdziale "Opcje zegara" opisano sposób wyboru tego oscylatora na zegar wewnętrzny. Oscylator można kalibrować przez zapis bajtu kalibracyjnego do rejestru OSCCAL. Jeśli oscylator wewnętrzny jest używany jako zegar mikrokontrolera, to oscylator licznika zegarowego (ang. Watchdog Oscillator) wciąż będzie używany dla licznika zegarowego oraz do odmierzania opóźnienia resetu. Zobacz do podrozdziału "Bajt kalibracyjny w ATtiny12". Przy zasilaniu mikrokontrolera napięciem 5V w temperaturze 25°C zaprogramowany wcześniej bajt kalibracyjny daje możliwość zmiany częstotliwości w zakresie ± 1% częstotliwości nominalnej.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x31 | CAL7 | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 | OSCCAL |

| Zapis/Odczyt | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Zapis bajtu kalibracyjnego pod ten adres spowoduje wyregulowanie wewnętrznego oscylatora w celu usunięcia odchyłek w generowanej częstotliwości. Gdy OSCCAL ma wartość zero, zostaje wybrana najniższa dostępna częstotliwość. Zapis niezerowej wartości do tego rejestru spowoduje wzrost częstotliwości wewnętrznego oscylatora. Zapisanie 0xFF do tego rejestru da najwyższą dostępną częstotliwość. Oscylator jest używany przy odmierzaniu czasu dostępu do pamięci EEPROM. Jeśli pamięć EEPROM jest zapisywana, nie kalibruj oscylatora powyżej 10% ponad częstotliwość nominalną. W przeciwnym razie zapis do EEPROM może się nie powieść. Poniższa tabela pokazuje zakres dla OSCCAL. Zwróć uwagę, że kalibracja ma na celu ustawienie częstotliwości oscylatora na 1,2 MHz, stąd dostrojenie go do innych wartości częstotliwości nie jest gwarantowane.

| Wartość OSCCAL |

Minimalna częstotliwość |

Maksymalna częstotliwość |

| 0x00 | 0,6 MHz | 1,2 MHz |

| 0x7F | 0,8 MHz | 1,7 MHz |

| 0xFF | 1,2 MHz | 2,5 MHz |

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.