|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

If you use Microchip copyrighted material solely for educational (non-profit) purposes falling under the “fair use” exception of the U.S. Copyright Act of 1976 then you do not need Microchip’s written permission. For example, Microchip’s permission is not required when using copyrighted material in: (1) an academic report, thesis, or dissertation; (2) classroom handouts or textbook; or (3) a presentation or article that is solely educational in nature (e.g., technical article published in a magazine).

https://www.microchip.com/about-us/legal-information/copyright-usage-guidelines

Mikrokontroler ATtiny11/12 udostępnia dwa bity blokowania LB1 i LB2 (ang. Lock Bits), które można pozostawić w stanie niezaprogramowanym (“1”) lub można je zaprogramować (“0”) w celu otrzymania dodatkowych własności, które opisuje poniższa tabela. Bity blokowania można wymazać tylko za pomocą rozkazu kasowania układu (ang. Chip Erase command).

| Bity blokowania pamięci |

Rodzaj ochrony | ||

| Tryb | LB1 | LB2 | |

| 1 | 1 | 1 | Brak ochrony pamięci. |

| 2 | 0 | 1 | Dalsze programowanie FLASH (i EEPROM w ATtiny12) jest wyłączone.(1) |

| 3 | 0 | 0 | Tak samo jak w trybie 2, lecz wyłączona jest również weryfikacja. |

ATtiny11 posiada pięć bitów bezpiecznikowych: FSTRT, RSTDISBL oraz CKSEL2:0 (3 bity).

FSTRT (ang. Fast Start – szybki start)

Poniższa tabela przedstawia wpływ tego bitu na czasy uruchamiania przy różnych opcjach zegarowych (VCC = 2,7V). Standardowo bit ten jest niezaprogramowany (“1”).

| Wybrana opcja zegara | Czas uruchamiania tTOUT | |

| FSTRT niezaprogramowany |

FSTRT zaprogramowany |

|

| Zewnętrzny kwarc | 67 ms | 4,2 ms |

| Zewnętrzny rezonator ceramiczny | 67 ms | 4,2 ms |

| Zewnętrzny kwarc o niskiej częstotliwości | 4,2 s | 4,2 s |

| Zewnętrzny oscylator RC | 4,2 ms | 67 μs |

| Wewnętrzny oscylator RC | 4,2 ms | 67 μs |

| Zewnętrzny zegar | 4,2 ms | 5 cykli od resetu, 2 cykle od wyłączenia |

RSTDISBL (ang. Reset Disable – wyłączenie zewnętrznego resetu)

Gdy RSTDISBL jest zaprogramowany (“0”), to funkcja zewnętrznego resetu na końcówce PB5 jest wyłączona i końcówka ta działa jako cyfrowe wejście. Standardowo bit ten jest niezaprogramowany (“1”).(1)

CKSEL2:0 (ang. Clock Select – wybór zegara)

Poniższa tabela przedstawia możliwe opcje zegara wybierane przez ustawienia tych bitów:. Standardową wartością bitów CKSEL2:0 jest “100”, wewnętrzny oscylator RC.

| Opcja zegarowa mikrokontrolera | ATtiny11: CKSEL2..0. |

| Zewnętrzny kwarc/rezonator ceramiczny | 111 |

| Zewnętrzny kwarc o niskiej częstotliwości | 110 |

| Zewnętrzny oscylator RC | 101 |

| Wewnętrzny oscylator RC | 100 |

| Zewnętrzny zegar | 000 |

| Zarezerwowane | pozostałe opcje |

| Uwaga: | "1" oznacza bit niezaprogramowany, "0" oznacza bit zaprogramowany |

Stan tych bitów bezpiecznikowych nie jest zmieniany przez kasowanie układu (ang. Chip Erase).

Uwaga: 1. Jeśli bit bezpiecznikowy RSTDISBL jest zaprogramowany, to programator powinien przyłożyć napięcie +12V do końcówki PB5, gdy ATtiny11 jest w trybie resetu przy włączeniu zasilania. Jeśli nie, to mikrokontroler może nie wejść w tryb programowania z powodu konfliktu wysterowania na końcówce PB0.

ATtiny12 posiada osiem bitów bezpiecznikowych: BODLEVEL, BODEN, SPIEN, RSTDISBL i CKSEL3:0 (4 bity). Wszystkie te bity bezpiecznikowe można programować w trybach wysokonapięciowego i niskonapięciowego programowania szeregowego. W trybie programowania zmiana bitu bezpiecznikowego nie wpływa na pełnioną przezeń funkcję, bit bezpiecznikowy zaczyna działać dopiero po zakończeniu programowania i uruchomieniu mikrokontrolera w trybie normalnej pracy.

BODLEVEL (ang. BOD Level, poziom wykrywania spadku napięcia)

Ten bit bezpiecznikowy wybiera poziom wykrywania spadku napięcia zasilającego (ang. Brown-out Detection, BOD) oraz zmienia czasy uruchomienia. Zobacz do podrozdziału "Wykrywanie spadku napięcia (ATtiny12)". Poniższa tabela przedstawia czasy uruchamiania mikrokontrolera w zależności od wybranego źródła zegara oraz ustawienia bitu bezpiecznikowego BODLEVEL:

| CKSEL3..0 | Źródło zegarowe | Czas uruchamiania VCC = 1,8V BODLEVEL niezaprogramowane |

Czas uruchamiania VCC = 2,7V BODLEVEL zaprogramowane |

| 1111 | Zewnętrzny kwarc/rezonator ceramiczny | 1K CK | 1K CK |

| 1110 | Zewnętrzny kwarc/rezonator ceramiczny | 3,6 ms + 1K CK | 4,2 ms + 1K CK |

| 1101 | Zewnętrzny kwarc/rezonator ceramiczny | 57 ms + 1K CK | 67 ms + 1K CK |

| 1100 | Zewnętrzny kwarc/rezonator ceramiczny | 16K CK | 16K CK |

| 1011 | Zewnętrzny kwarc/rezonator ceramiczny | 3,6 ms + 16K CK | 4,2 ms + 16K CK |

| 1010 | Zewnętrzny kwarc/rezonator ceramiczny | 57 ms + 16 CK | 67 ms + 16K CK |

| 1001 | Kwarc o niskiej częstotliwości | 57 ms + 1K CK | 67 ms + 16K CK |

| 1000 | Kwarc o niskiej częstotliwości | 57 ms + 32K CK | 67 ms + 16K CK |

| 0111 | Zewnętrzny oscylator RC | 6 CK | 6 CK |

| 0110 | Zewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0101 | Zewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0100 | Wewnętrzny oscylator RC | 6 CK | 6 CK |

| 0011 | Wewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0010 | Wewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0001 | Zewnętrzny zegar | 6 CK | 6 CK |

| 0000 | Zewnętrzny zegar | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

CK – cykl zegarowy

Standardową wartością BODLEVEL jest stan zaprogramowany (“0”).

BODEN (ang. BOD Enable, włączenie wykrywania spadku napięcia zasilającego)

Gdy bit bezpiecznikowy BODEN jest zaprogramowany (“0”), włączone zostaje wykrywanie spadków napięcia zasilania. Zobacz do podrozdziału "Wykrywanie spadku napięcia (ATtiny12)". Standardową wartością jest stan niezaprogramowany (“1”)

SPIEN (ang. SPI Enable, włączenie interfejsu niskonapięciowego programowania szeregowego SPI)

Gdy bit bezpiecznikowy SPIEN jest zaprogramowany (“0”), zostaje uaktywniony interfejs SPI niskonapięciowego programowania szeregowego i ładowania danych. Standardową wartością jest stan zaprogramowany (“0”). Skasowanie tego stanu w stan niezaprogramowany podczas trybu niskonapięciowego programowania szeregowego uniemożliwi przyszłe próby programowania mikrokontrolera w układzie ISP (ang. In-System Programming, programowanie w układzie aplikacyjnym).

RSTDISBL (ang. Reset Disable, wyłączenie resetu zewnętrznego)

Gdy bit bezpiecznikowy RSTDISBL jest zaprogramowany (“0”), to zewnętrzna funkcja resetu końcówki PB5 jest wyłączona.(1) Standardową wartością jest stan niezaprogramowany (“1”). Zaprogramowanie tego bitu w trybie niskonapięciowego programowania szeregowego uniemożliwi przyszłe próby programowania SPI (ang. In-System Programming, programowanie w układzie aplikacyjnym).

CKSEL3:0 (ang. Clock Select, wybór zegara)

Poniższe tabele pokazują ustawienia bitów bezpiecznikowych dla różnych opcji zegarowych:

| Opcja zegarowa mikrokontrolera | CKSEL3:0 |

| Zewnętrzny kwarc/rezonator ceramiczny | 1111 ... 1010 |

| Zewnętrzny kwarc o niskiej częstotliwości | 1001 ... 1000 |

| Zewnętrzny oscylator RC | 0111 ... 0101 |

| Wewnętrzny oscylator RC | 0100 ... 0010 |

| Zewnętrzny zegar | 0001 ... 0000 |

| Zarezerwowane | - |

| Uwaga: | "1" oznacza bit niezaprogramowany, "0" oznacza bit zaprogramowany |

| CKSEL3..0 | Źródło zegarowe | Czas uruchamiania VCC = 1,8V BODLEVEL niezaprogramowane |

Czas uruchamiania VCC = 2,7V BODLEVEL zaprogramowane |

| 1111 | Zewnętrzny kwarc/rezonator ceramiczny | 1K CK | 1K CK |

| 1110 | Zewnętrzny kwarc/rezonator ceramiczny | 3,6 ms + 1K CK | 4,2 ms + 1K CK |

| 1101 | Zewnętrzny kwarc/rezonator ceramiczny | 57 ms + 1K CK | 67 ms + 1K CK |

| 1100 | Zewnętrzny kwarc/rezonator ceramiczny | 16K CK | 16K CK |

| 1011 | Zewnętrzny kwarc/rezonator ceramiczny | 3,6 ms + 16K CK | 4,2 ms + 16K CK |

| 1010 | Zewnętrzny kwarc/rezonator ceramiczny | 57 ms + 16 CK | 67 ms + 16K CK |

| 1001 | Kwarc o niskiej częstotliwości | 57 ms + 1K CK | 67 ms + 16K CK |

| 1000 | Kwarc o niskiej częstotliwości | 57 ms + 32K CK | 67 ms + 16K CK |

| 0111 | Zewnętrzny oscylator RC | 6 CK | 6 CK |

| 0110 | Zewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0101 | Zewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0100 | Wewnętrzny oscylator RC | 6 CK | 6 CK |

| 0011 | Wewnętrzny oscylator RC | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

| 0010 | Wewnętrzny oscylator RC | 5,7 ms + 6 CK | 67 ms + 6K CK |

| 0001 | Zewnętrzny zegar | 6 CK | 6 CK |

| 0000 | Zewnętrzny zegar | 3,6 ms + 6 CK | 4,2 ms + 6K CK |

CK – cykl zegarowy

Standardową wartością jest "0010", wewnętrzny oscylator RC z długim czasem uruchamiania.

Stan bitów bezpiecznikowych nie jest zmieniany podczas kasowania układu (ang. Chip Erase).

Uwaga: 1. Jeśli bit bezpiecznikowy RSTDISBL jest zaprogramowany, to programator powinien przyłożyć do końcówki PB5 napięcie +12V, gdy ATtiny12 jest w trybie resetu przy włączeniu zasilania. Jeśli nie, to układ może nie wejść w tryb programowania z powodu konfliktów w sterowaniu końcówek PB0 i PB5.

Wszystkie mikrokontrolery firmy Atmel

(obecnie przejętej przez

firmę Microchip) posiadają trójbajtowy kod sygnaturowy, który

identyfikuje mikrokontroler. Te trzy bajty przechowywane są w

oddzielnej przestrzeni adresowej.

Dla ATtiny11 są to:

Dla ATtiny12(1) są to:

Uwaga: 1. Gdy oba bity blokujące są zaprogramowane (tryb blokowania 3), bajty sygnaturowe nie można odczytywać w niskonapięciowym trybie programowania szeregowego. Odczyt bajtów sygnaturowych zwróci w takim przypadku: 0x00, 0x01 i 0x02.

ATtiny12 posiada jednobajtową wartość kalibracyjną dla wewnętrznego oscylatora RC. Ten bajt przebywa w górnym bajcie słowa pod adresem 0x000 w przestrzeni adresowej sygnatur. Podczas programowania pamięci zewnętrzny programator musi odczytać tę komórkę i zaprogramować jej wartość w wybranej komórce normalnej pamięci FLASH programu. Przy starcie oprogramowanie użytkownika musi odczytać tę komórkę FLASH i zapisać jej zawartość w rejestrze OSCCAL.

Mikrokontroler Atmel ATtiny11 oferuje 1 KB wewnętrznej pamięci FLASH dla programu. Pamięć ta jest wymazana w układach dostępnych w handlu (tj. zawiera w każdej komórce wartość 0xFF, czyli wszystkie bity w stanie 1) i gotowa do zaprogramowania.

Mikrokontroler ten obsługuje tryb wysokonapięciowego (12V) programowania szeregowego. Ze źródła napięcia 12V pobierany jest bardzo mały prąd (<1 mA) podczas programowania.

Pamięć programu w ATtiny11 jest programowana bajt po bajcie.

Mikrokontroler Atmel ATtiny12 oferuje 1 KB pamięci FLASH dla programu programowanej w układzie docelowym oraz 64 bajty reprogramowalnej pamięci EEPROM dla danych.

ATtiny12 jest sprzedawany z wymazaną zawartością pamięci FLASH programu i pamięci EEPROM danych (tj. wszystkie komórki przechowują wartość 0xFF), które są gotowe do zaprogramowania.

Ten mikrokontroler obsługuje tryby wysokonapięciowego (12V) i niskonapięciowego programowania szeregowego. Napięcie +12V jest używane tylko do uaktywnienia trybu programowania i nie jest z niego pobierany żaden znaczący prąd. Tryb niskonapięciowego programowania szeregowego udostępnia wygodny sposób ładowania programu oraz danych do ATtiny12 w systemie użytkownika.

Pamięci programu i danych są w ATtiny12 programowane bajt po bajcie w obu trybach programowania. Dla EEPROM udostępniony jest cykl samokasowania w obrębie czasu instrukcji zapisu w trybie niskonapięciowego programowania szeregowego.

Podczas programowania napięcie zasilające musi być zgodne z napięciami podanymi w poniższej tabeli:

| Mikrokontroler | Programowanie szeregowe | |

| niskonapięciowe | wysokonapięciowe | |

| ATtiny11L | nie ma zastosowania | 4,5...5,5,V |

| ATtiny11 | nie ma zastosowania | 4,5...5,5,V |

| ATtiny12V | 2,2...5,5V | 4,5...5,5,V |

| ATtiny12L | 2,7...5,4V | 4,5...5,5,V |

| ATtiny12 | 4,0...5,5V | 4,5...5,5,V |

Aby zaprogramować i zweryfikować mikrokontroler ATtiny11/12 w trybie wysokonapięciowego programowania szeregowego, zaleca się stosowanie poniższych kroków (zobacz na tabelę formatów instrukcji):

Gdy dane szeregowe są zapisywane lub odczytywane z ATtiny11/12, dane są taktowane narastającym zboczem zegara szeregowego.

| Uwaga: | MSB (ang. Most Significant Bit, najstarszy bit) |

| LSB (ang. Least Significant Bit, najmłodszy bit) |

| Instrukcja | Format instrukcji | Uwagi | ||||

| Inst.1 | Inst.2 | Inst.3 | Inst.4 | |||

| Chip Erase Kasowanie układu |

PB0 PB1 PB2 |

0_1000_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

Po instr.4 czekaj, aż PB2 przyjmie stan wysoki, co będzie oznaczało zakończenie cyklu kasowania układu. |

| Write FLASH High and Low Address Adres zapisu do FLASH |

PB0 PB1 PB2 |

0_0001_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_000a_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_bbbb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

|

Powtarzaj instr.2 dla nowej 256-bajtowej strony. Powtarzaj instr.3 dla każdego nowego adresu.. |

| Write FLASH Low byte Zapis dolnego bajtu do FLASH |

PB0 PB1 PB2 |

0_iiii_iiii_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 0_0000_0000_00 |

|

Po instr.3 czekaj, aż

PB2 przejdzie w stan wysoki. Powtarzaj wszystkie 3 instrukcje dla każdego nowego adresu. |

| Write FLASH High byte Zapis górnego bajtu do FLASH |

PB0 PB1 PB2 |

0_iiii_iiii_00 0_0011_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 0_0000_0000_00 |

|

Po instr.3 czekaj, aż PB2 przejdzie w stan wysoki. Powtarzaj wszystkie 3 instrukcje dla każdego nowego adresu. |

| Read FLASH High and Low Address Adres odczytu z FLASH |

PB0 PB1 PB2 |

0_0000_0010_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_000a_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_bbbb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

|

Powtarzaj instr.2 i instr.3 dla każdego nowego adresu. |

| Read FLASH Low byte Odczyt dolnego bajtu z FLASH |

PB0 PB1 PB2 |

00_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 o_oooo_ooox_xx |

|

|

Powtarzaj instr.1 i instr.2 dla każdego nowego adresu. |

| Read FLASH High byte Odczyt górnego bajtu z FLASH |

PB0 PB1 PB2 |

0_0000_0000_00 0_0111_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 o_oooo_ooox_xx |

|

|

Powtarzaj instr.1 i

instr.2 dla każdego nowego adresu. |

| Write EEPROM Low Address Adres zapisu do EEPROM (ATtiny12) |

PB0 PB1 PB2 |

0_0001_0001_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_00bb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

|

|

Powtarzaj instr.2 dla każdego nowego adresu. |

| Write EEPROM byte Zapis bajtu do EEPROM (ATtiny12) |

PB0 PB1 PB2 |

0_iiii_iiii_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 0_0000_0000_00 |

|

Po instr.3 czekaj, aż

PB2 przyjmie stan wysoki. |

| Read EEPROM Low Address Adres odczytu z EEPROM (ATtiny12) |

PB0 PB1 PB2 |

0_0000_0011_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_00bb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

|

|

Powtarzaj instr.2 dla każdego nowego adresu. |

| Read EEPROM byte Odczyt bajtu z EEPROM (ATtiny12) |

PB0 PB1 PB2 |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 o_oooo_ooox_xx |

|

|

Powtarzaj instr.2 dla każdego nowego adresu. |

| Write Fuse bits Zapis bitów bezpiecznikowych (ATtiny11) |

PB0 PB1 PB2 |

0_0100_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0007_6543_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Odczekaj tWLWH_PFB

po instr.3, aby cykl zapisu bitów bezpiecznikowych zakończył się. Zapisz 7...3 = “0”, aby zaprogramować bit bezpiecznikowy. |

| Write Fuse bits Zapis bitów bezpiecznikowych (ATtiny12) |

PB0 PB1 PB2 |

0_0100_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_CBA9_8543_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Po instr.4 zaczekaj, aż

PB2 przejdzie w stan wysoki. Zapisz: C...A, 9, 8, 5...3 = “0”, aby zaprogramować bit bezpiecznikowy. |

| Write Lock bits Zapis bitów blokujących |

PB0 PB1 PB2 |

0_0010_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0210_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 0_0000_0000_00 |

Po instr.4 zaczekaj, aż

PB2 przejdzie w stan wysoki. Zapisz: 2, 1 = “0”, aby zaprogramować bit bezpiecznikowy. |

| Read Fuse bits Odczyt bitów bezpiecznikowych (ATtiny11) |

PB0 PB1 PB2 |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xx76_543x_xx |

|

Odczyt 7...3 = “0” oznacza, iż dany bit bezpiecznikowy jest zaprogramowany. |

| Read Fuse bits Odczyt bitów bezpiecznikowych (ATtiny12) |

PB0 PB1 PB2 |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 C_BA98_543x_xx |

|

Odczyt C...A,

9, 8,

5... 3 = “0” oznacza, iż dany bit bezpiecznikowy jest zaprogramowany. |

| Read Lock bits Odczyt bitów blokujących |

PB0 PB1 PB2 |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 x_xxxx_21xx_xx |

|

Odczyt 2...1 = “0” oznacza, iż dany bit blokujący jest zaprogramowany. |

| Read Signature Bytes Odczyt bajtów sygnaturowych |

PB0 PB1 PB2 |

0_0000_1000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_00bb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 o_oooo_ooox_xx |

Powtarzaj instr.2 ...

instr.4 dla każdego adresu bajtu sygnaturowego. |

| Read Calibration Byte Odczyt bajtu kalibracyjnego (ATtiny12) |

PB0 PB1 PB2 |

0_0000_1000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 o_oooo_ooox_xx |

|

| Uwaga: | a

= górne bity adresu b = dolne bity adresu i = dane wejściowe o = dane wyjściowe x = wartość obojętna 1 = Bit blokowania 1 2 = Bit blokowania 2 3 = bit bezpiecznikowy CKSEL0 4 = bit bezpiecznikowy CKSEL1 5 = bit bezpiecznikowy CKSEL2 9, 6 = bit bezpiecznikowy RSTDISBL 7 = bit bezpiecznikowy FSTRT 8 = bit bezpiecznikowy CKSEL3 A = bit bezpiecznikowy SPIEN B = bit bezpiecznikowy BODEN C = bit bezpiecznikowy BODLEVEL |

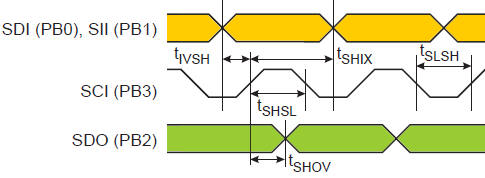

| Symbol | Parametr | Min. | Typ. | Max. | Jednostka |

| tSHSL | SCI (PB3) szerokość impulsu 1 | 100 | ns | ||

| tSLSH | SCI (PB3) szerokość impulsu 0 | 100 | ns | ||

| tIVSH | Dane SDI (PB0),

SII

(PB1) ważne przy zboczu narastającym SCI (PB3) |

50 | ns | ||

| tSHIX | Przetrzymanie danych SDI (PB0), SII (PB1) po zboczu narastającym SCI (PB3) |

50 | ns | ||

| tSHOV | Ważność danych SDO (PB2)

po zboczu narastającym SCI (PB3) |

10 | 16 | 32 | ns |

| tWLWH_PFB | Oczekiwanie po instr.3 na zapis bitów bezpiecznikowych |

1,7 | 2,5 | 3,4 | ms |

Obie pamięci programu i danych mogą być programowane przy pomocy magistrali SPI, gdy końcówka RESET jest zwarta do masy GND. Interfejs szeregowy składa się z końcówek SCK, MOSI (wejście) oraz MISO (wyjście).

Po sprowadzeniu RESET do poziomu niskiego musi zostać wykonana instrukcja uaktywniająca programowanie, zanim będą mogły być wykonane instrukcje programowania/kasowania.

Jeśli zostanie wykonany tylko jeden raz rozkaz kasowania układu (ang. Chip Erase command) w trybie niskonapięciowego programowania szeregowego, to po skasowaniu jeden bajt może wciąż być zaprogramowany w pamięci FLASH po kasowaniu. Poniższy algorytm gwarantuje, iż pamięć FLASH zostanie całkowicie wymazana:

Dla EEPROM jest udostępniony cykl samokasowania w obrębie czasu przeznaczonego na instrukcję zapisu i nie ma potrzeby wykonywać wcześniej instrukcji kasowania układu. Instrukcja ta umieszcza we wszystkich komórkach pamięci programu i pamięci EEPROM wartość 0xFF.

Pamięć programu i pamięć EEPROM posiadają oddzielne przestrzenie adresowe: 0x0000 ... 0x01FF dla pamięci programu (512 komórek 16 bitowych, co daje 1024 bajty, czyli 1 KB) i 0x000 ... 0x03F dla pamięci EEPROM (64 bajty).

Podczas niskonapięciowego programowania szeregowego mikrokontroler może być taktowany dowolną opcją zegarową.

Dla wejścia zegara szeregowego (ang. Serial Clock, SCK) zdefiniowane są następujące minimalne czasy okresów niskich i wysokich:

Niski: > 2 cykle zegara mikrokontrolera

Wysoki: > 2 cykle zegara mikrokontrolera

Gdy dane szeregowe są zapisywane do ATtiny12, taktowanie odbywa się przy narastającym zboczu sygnału zegarowego SCK. Gdy dane są odczytywane z ATtiny12, ich taktowanie odbywa się przy opadającym zboczu SCK.

Do programowania i weryfikacji ATtiny12 w trybie programowania szeregowego zaleca się poniższą sekwencję operacji:

Gdy bajt jest programowany w pamięci FLASH lub w EEPROM, odczytanie zawartości lokacji, która jest właśnie programowana, da wynik 0xFF. Gdy pamięć jest gotowa na zapis nowego bajtu, programowana wartość zostanie odczytana poprawnie. Używa się tego sposobu do określania, czy następny bajt może zostać zapisany. To nie zadziała dla wartości 0xFF, zatem przy programowaniu tej wartości , należy odczekać przynajmniej przez czas odpowiednio tWD_FLASH lub tWD_EEPROM przed programowaniem następnego bajtu. Ponieważ wykasowany układ zawiera 0xFF we wszystkich komórkach, można pominąć programowanie komórek, które mają zawierać 0xFF. Nie dotyczy to sytuacji, gdy pamięć EEPROM jest ponownie programowana bez kasowania zawartości całego mikrokontrolera. W tym przypadku nie można używać podglądu danych dla wartości 0xFF i należy odczekać przynajmniej przez czas tWD_EEPROM przed programowaniem następnego bajtu.

| Uwaga: | MSB (ang. Most Significant Bit, najstarszy bit) |

| LSB (ang. Least Significant Bit, najmłodszy bit) |

| Instrukcja | Format instrukcji | Operacja | |||

| Bajt 1 | Bajt 2 | Bajt 3 | Bajt 4 | ||

| Programming

Enable Uaktywnienie programowania |

1010 1100 |

0101 0011 |

xxxx xxxx |

xxxx xxxx |

Gdy

końcówka RESET

jest wysterowana stanem niskim, włącza tryb programowania szeregowego. |

| Chip Erase Kasowanie układu |

1010 1100 |

100x xxxx |

xxxx xxxx |

xxxx xxxx |

Kasowanie zawartości pamięci FLASH i EEPROM. |

| Read Program

Memory Odczyt pamięci programu |

0010 H000 |

xxxx xxxa |

bbbb bbbb |

oooo oooo |

Odczyt górnego lub

dolnego (w zależności od H) bajtu pamięci programu ze słowa pod adresem a:b. |

| Write Program

Memory Zapis pamięci programu |

0100 H000 |

xxxx xxxa |

bbbb bbbb |

iiii iiii |

Zapis górnego lub

dolnego (w zależności od H) bajtu pamięci programu do słowa pod adresem a:b. |

| Read EEPROM

Memory Odczyt pamięci EEPROM |

1010 0000 |

xxxx xxxx |

xxbb bbbb |

oooo oooo |

Odczyt danych

o

z pamięci EEPROM spod adresu b. |

| Write EEPROM

Memory Zapis pamięci EEPROM |

1100 0000 |

xxxx xxxx |

xxbb bbbb |

iiii iiii |

Zapis danych

i

do pamięci EPROM pod adres b. |

| Write Lock

Bits Zapis bitów blokowania |

1010 1100 |

1111 1211 |

xxxx xxxx |

xxxx xxxx |

Zapis bitów blokowania. Ustaw 2,1 = 0, aby zaprogra- mować bit blokowania. |

| Read Lock

Bits Odczyt bitów blokowania |

0101 1000 |

xxxx xxxx |

xxxx xxxx |

xxxx x21x |

Odczyt bitów

blokowania. "0" = zaprogramowany, "1" = niezaprogramowany. |

| Read

Signature Bytes Odczyt bajtów sygnaturowych |

0011 0000 |

xxxx xxxx |

0000 00bb |

oooo oooo |

Odczyt bajtu

sygnaturowego o spod adresu bb. |

| Read

Calibration Byte Odczyt bajtu kalibracyjnego |

0011 1000 |

xxxx xxxx |

0000 0000 |

oooo oooo |

|

| Write Fuse

Bits Zapis bitów bezpiecznikowych |

1010 1100 |

xxxx xxxx |

101x xxxx |

A987 6543 |

Ustaw bity

A,9

... 3 = 0, aby je zaprogramować. |

| Read Fuse

Bits Odczyt bitów bezpiecznikowych |

0101 0000 |

xxxx xxxx |

xxxx xxxx |

A987 6543 |

Odczyt bitów

bezpiecznikowych. "0" = zaprogramowany, "1" = niezaprogramowany. |

| Symbol | Parametr | Min. | Typowo | Max. | Jednostka |

| 1/tCLCL | Częstotliwość oscylatora (VCC = 2,2 ... 2,7V) | 0 | 1 | MHz | |

| tCLCL | Okres oscylatora (VCC = 2,2 ... 2,7V) | 1000 | ns | ||

| 1/tCLCL | Częstotliwość oscylatora (VCC = 2,7 ... 4,0V) | 0 | 4 | MHz | |

| tCLCL | Okres oscylatora (VCC = 2,7 ... 4,0V) | 250 | ns | ||

| 1/tCLCL | Częstotliwość oscylatora (VCC = 4,0 ... 5,5V) | 0 | 8 | MHz | |

| tCLCL | Okres oscylatora (VCC = 4,0 ... 5,5V) | 125 | ns | ||

| tSHSL | Szerokość impulsu 1 SCK | 2tCLCL | ns | ||

| tSLSH | Szerokość impulsu 0 SCK | 2tCLCL | ns | ||

| tOVSH | Czas ustalania MOSI przed SCK 1 | tCLCL | ns | ||

| tSHOX | Czas utrzymywania MOSI po SCK 1 | 2tCLCL | ns | ||

| tSLIV | Czas ważności MISO po SCK 0 | 10 | 16 | 32 | ns |

| Symbol | Minimalny czas opóźnienia |

| tWD_ERASE | 6,8 ms |

| Symbol | Minimalny czas opóźnienia |

| tWD_FLASH | 3,4 ms |

| tWD_EEPROM | 6,8 ms |

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.