| Serwis Edukacyjny w I-LO w Tarnowie

Materiały dla uczniów liceum |

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

| Serwis Edukacyjny w I-LO w Tarnowie

Materiały dla uczniów liceum |

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

W warsztacie elektronika potrzebne są różne urządzenia pomiarowe. Próbnik logiczny, zwany również sondą logiczną, pozwala sprawdzać poziomy logiczne w testowanym układzie. Pomiaru takiego możesz dokonać również zwykłym miernikiem, jednakże specjalizowany próbnik jest wygodniejszy. Nasz próbnik będzie pokazywał stany logiczne 0 i 1, brak sygnału oraz przebieg prostokątny o różnym stopniu wypełnienia. Układ pochodzi z Elektroniki dla wszystkich 8/98. Zmodyfikowałem go, usuwając wskaźnik 7-mio segmentowy i wstawiając zamiast niego diody LED czerwoną, zieloną i żółtą. Układ ten wybrałem, ponieważ poćwiczymy na tym przykładzie tworzenie płytki dwustronnej w Eagle.

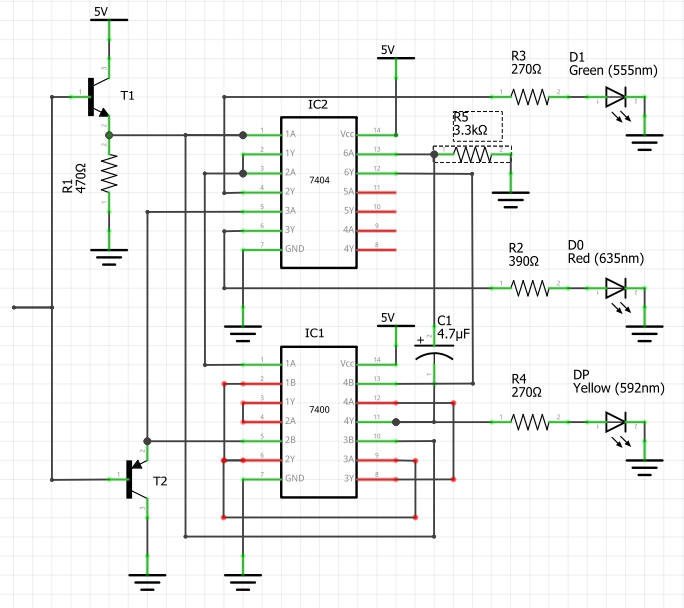

Najpierw schemat ideowy próbnika:

Aby zrozumieć zasadę działania tego układu, musisz poznać funkcje jego elementów składowych. Zacznijmy od tranzystorów wejściowych.

Tranzystor T1 pracuje w układzie tzw. wtórnika emiterowego. Na wyjściu pojawia się napięcie wejściowe pomniejszone o spadek napięcia na złączu baza-emiter (około 0,7V). Odpowiada ono logicznie napięciu wejściowemu. Jeśli baza nie jest podłączona do napięcia, to tranzystor nie przewodzi na złączu emiter-kolektor i napięcie wyjściowe jest praktycznie równe 0V.

Tranzystor T2 jest tranzystorem p-n-p. Jeśli baza nie jest wysterowana żadnym napięciem, to tranzystor nie przewodzi na złączu emiter-kolektor i napięcie wyjściowe będzie traktowane przez bramki TTL jako stan wysoki. Gdy bazę wysterujemy napięciem wysokim, to tranzystor będzie wciąż zatkany. Tranzystor zacznie przewodzić na złączu emiter-kolektor, gdy napięcie na bazie będzie niskie. Wtedy tranzystor "zewrze" wyjście z masą i na wyjściu pojawi się stan niski.

Podsumowując, jeśli wejście TEST nie jest podłączone do napięcia, to na wyjściu z T1 panuje stan logiczny 0, a na wyjściu z T2 jest stan logiczny 1. Jeśli wejście TEST zostanie podłączone do napięcia o poziomie TTL, to na wyjściach obu układów pojawi się napięcie o takim samym poziomie logicznym.

Tranzystor T1 steruje wejściem inwertera I1. Dwa kolejne inwertery nie odwracają stanu logicznego, zatem na wyjściu inwertera I2 panuje taki sam stan logiczny, jak na wejściu inwertera I1. Dioda D1 zaświeci się, jeśli wejście będzie w stanie wysokim.

Tranzystor T2 steruje wejściem inwertera I3. Na wyjściu panuje stan przeciwny do wejściowego. Dioda D0 zapali się, jeśli na wejściu będzie stan logiczny 0.

Z powyższego opisu wynika:

Pozostałe bramki są wykorzystywane do wykrywania impulsów oraz przebiegu okresowego. Tworzą one dwa przerzutniki.

Bramki NAND N1 i N2 są połączone w układzie przerzutnika SR. Podobny przerzutnik zbudowaliśmy z tranzystorów w poprzednim projekcie. Przerzutnik SR (ang. Set-Reset Flip-Flop) posiada dwa wejścia: ustawiające S (ang. Set) i zerujące R (ang. Reset). Kreseczki nad symbolami wejść informują, iż stanem aktywnym jest stan niski, co jest charakterystyczne dla przerzutników zbudowanych z bramek NAND. Tabelka stanów jest następująca:

| S | R | Q |

| 1 | 1 | Qn-1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 0 | 0 | N |

Qn-1 oznacza stan,

w którym przerzutnik znajdował się poprzednio

N oznacza niedozwolony

stan wejść, tzn. stan wyjścia Q jest nieokreślony.

Z powyższej tabelki wynika, że przerzutnik pamięta stan, gdy oba wejścia są w stanie wysokim. Oba wejścia nie powinny się znaleźć jednocześnie w stanie 0.

W naszym próbniku przerzutnik SR jest wykorzystywany do zapamiętania stanu wejściowego:

Wynika z tego, iż wyjście Q przyjmuje zawsze stan przeciwny do stanu wejściowego.

Bramka N3 wykorzystuje przerzutnik oraz tranzystor T1 do wygenerowania krótkiego impulsu ujemnego. Przerzutnik SR nie przełącza się w nowy stan natychmiast, musi upłynąć pewien czas związany z propagacją (przejściem) sygnału z wejścia bramki na jej wyjście. Trwa to kilka nanosekund. Zjawisko powoduje, iż przy zmianie stanu wejścia TEST z 0 na 1 (zbocze dodatnie) przez krótki czas na obu wejściach bramki N3 pojawi się stan logiczny 1 (1 z wyjścia Q przerzutnika SR oraz 1 z wyjścia tranzystora T1), a to z kolei spowoduje wygenerowanie na jej wyjściu krótkiego impulsu ujemnego (o stanie 0). Po kilku nanosekundach przerzutnik SR ustawi wyjście Q w stan 0 (stan przeciwny do stanu wejścia TEST) i na wejściach N3 będą różne stany (0 z wyjścia Q przerzutnika i 1 z tranzystora T1), zatem wyjście N3 powróci do stanu 1.

Bramki N4 i I4 tworzą przerzutnik monostabilny. W normalnym stanie wejście wyzwalające bramki N4 jest w stanie wysokim. Gdy kondensator C1 jest rozładowany, na wejściu I4 panuje stan niski 0. Na wyjściu I4 jest stan logiczny 1, który steruje drugim wejściem bramki N4. Ponieważ na obu jej wejściach panuje stan 1, to na wyjściu N4 jest stan 0 i dioda DP nie świeci.

Gdy na wejście wyzwalające N4 zostanie podany impuls ujemny, spowoduje to ustawienie wyjścia tej bramki w stan 1. Dioda DP zaświeci się. Dodatkowo wzrośnie napięcie na wejściu I4 poprzez kondensator, który zacznie się ładować poprzez opornik R2. Wzrost napięcia na wejściu I4 spowoduje stan logiczny 0 na wyjściu. ponieważ wejście wyzwalające N4 wraca szybko do stanu 1, na wejściach N4 są przeciwne stany logiczne, a to podtrzymuje stan 1 na wyjściu N4 i dioda DP się wciąż świeci, pomimo zaniku impulsu wyzwalającego. Jednakże w miarę upływu czasu napięcie na kondensatorze C1 rośnie, a to z kolei powoduje spadek napięcia na wejściu inwertera I4. Gdy napięcie osiągnie poziom przełączania, na wyjściu I4 pojawi się stan logiczny 1. Oba wejścia N4 będą wtedy w stanie logicznym 1, i na wyjściu N4 pojawi się stan 0, dioda DP zgaśnie.

Przerzutnik monostabilny jest tutaj wykorzystywany do wydłużania czasu trwania impulsu przy zboczu dodatnim sygnału na wejściu TEST. Dzięki temu dioda DP zauważalnie błyśnie przy zmianie sygnału wejściowego z 0 na 1. Jeśli sygnał będzie się zmieniać cyklicznie odpowiednio szybko, to dioda będzie świecić ciągle. Pozwala to wykrywać impulsy o różnej częstotliwości.

Możemy teraz podsumować działanie naszego testera (M oznacza mruganie, C oznacza ciągłe świecenie diody DP):

| D0 | D1 | DP | Funkcja |

| brak sygnału | |||

| stan logiczny 0 | |||

| stan logiczny 1 | |||

| C | impulsy o wypełnieniu 50% | ||

| C | impulsy o wypełnieniu mniejszym od 50% | ||

| M | stan 0 z pojedynczymi impulsami dodatnimi | ||

| C | impulsy o wypełnieniu większym od 50% | ||

| M | stan 1 z pojedynczymi impulsami ujemnymi |

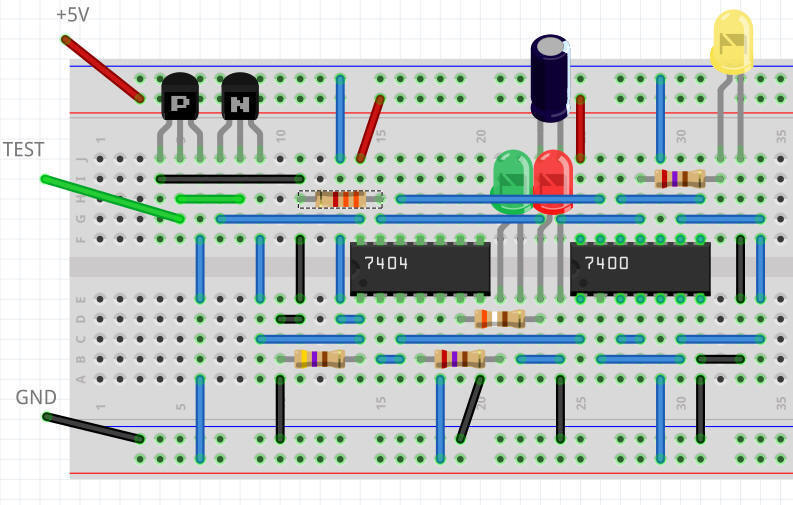

Przed przystąpieniem do projektowania układu, sprawdzimy jego działanie na płytce stykowej. Wykorzystamy program Fritzing do skonfigurowania połączeń. Najpierw tworzymy schemat ideowy.

Skompletujmy elementy elektroniczne:

|

||||||||||||||||||||||||||||||||||||||||||

7400 |

||||||||||||||||||||||||||||||||||||||||||

7404 |

Kondensator 100nF nie jest potrzebny na tym etapie. Służy on jedynie do eliminacji zakłóceń.

Następnie w programie Fritzing tworzymy połączenia dla płytki stykowej:

Fritzing rysuje przewody zawsze na wierzchu, dlatego na powyższym rysunku przykrywają one diody LED zieloną i czerwoną. W rzeczywistości przewody te mają iść po powierzchni płytki stykowej. Do testowania sygnałów można zastosować dwa niewykorzystywane inwertery NOT w układzie 7404. Na wyjściach tych inwerterów (nóżki 8 i 10) panuje stan logiczny 0. Jeśli wejście inwertera połączymy z masą, to na jego wyjściu pojawi się stan 1:

Dwie bramki NOT można również wykorzystać do utworzenia prostego generatora impulsów prostokątnych:

Dla nowszych układów 7404 (np. 74HCT04, 74LS04) użyj:

| R = 1k C = 4,7µF |

W starszych układach należy zmniejszyć R do 270...470Ω. Generator pozwoli przetestować funkcję wykrywania impulsów.

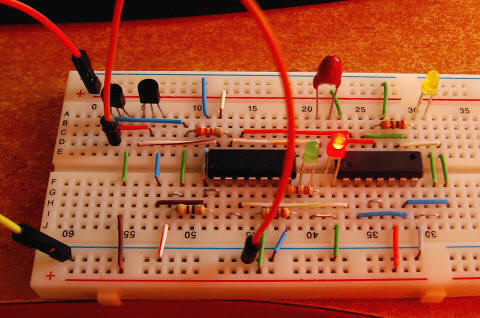

Wejście TEST zwarte do masy, stan logiczny 0 |

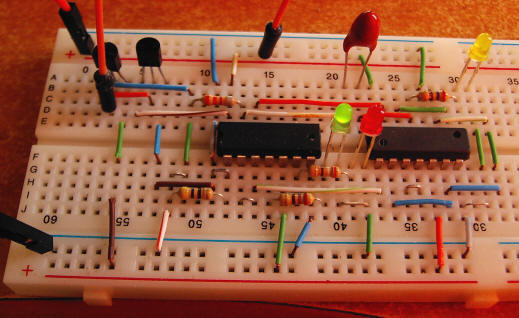

Wejście TEST zwarte do +5V, stan logiczny 1 |

Gdy zmontujesz i uruchomisz prototyp próbnika na płytce stykowej, możesz przystąpić do tworzenia właściwego układu elektronicznego. Nie pomijaj tego kroku - zaoszczędzisz mnóstwo czasu, jeśli się okaże, że twój układ posiada błędy i nie działa prawidłowo. Prototyp daje ci tę pewność. Gotowy próbnik utworzymy w dwóch wersjach: przewlekanej THT i wykorzystującej montaż powierzchniowy SMT.

Uruchom Eagle.

Otwórz katalogi Projects i eagle:

Kliknij prawym przyciskiem myszki w katalog eagle i z menu kontekstowego wybierz opcję New Project. Nowemu projektowi nadaj nazwę próbnik_ttl:

Zwróć uwagę, że nowy projekt został automatycznie otwarty – przy jego nazwie pojawiło się zielone kółko.

Kliknij prawym przyciskiem myszki projekt próbnik_ttl i z menu wybierz Edit Description:

Do edytora opisu wprowadź poniższy tekst (lub wymyśl coś swojego):

Zatwierdź opis. Projekt został utworzony. W następnych rozdziałach zajmiemy się schematami, płytkami PCB oraz wykonaniem próbnika.

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.