|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

If you use Microchip copyrighted material solely for educational (non-profit) purposes falling under the “fair use” exception of the U.S. Copyright Act of 1976 then you do not need Microchip’s written permission. For example, Microchip’s permission is not required when using copyrighted material in: (1) an academic report, thesis, or dissertation; (2) classroom handouts or textbook; or (3) a presentation or article that is solely educational in nature (e.g., technical article published in a magazine).

https://www.microchip.com/about-us/legal-information/copyright-usage-guidelines

W rozdziale pojawia się termin angielski Output Compare, który odnosi się do zmiany stanu wybranej końcówki, jeśli wewnętrzny licznik odmierzy odpowiedni czas. Odbywa się to w ten sposób, iż stan licznika jest porównywany z rejestrem przechowującym znacznik czasu. Gdy licznik osiągnie wartość znacznika czasu, występuje zgodność porównania (ang. Compare Match) i w tym momencie mikrokontroler może wykonać różne operacje, np. zmienić stan logiczny określonej końcówki. Pozwala to generować różne przebiegi czasowe. Ponieważ nie spotkałem dobrego tłumaczenia dla terminu Output Compare, postanowiłem go zachować w oryginalnej postaci.

Rejestr timera/licznika (TCNT0) oraz rejestry Output Compare (OCR0A i OCR0B) są rejestrami 8-bitowymi. Wszystkie sygnały żądań przerwań są widoczne w rejestrze znaczników przerwań timera (ang. Timer Interrupt Flag Register, TIFR). Wszystkie przerwania są indywidualnie maskowane za pomocą rejestru maski przerwań timera (ang. Timer Interrupt Mask Register, TIMSK). Rejestry TIFR i TIMSK nie są pokazane na obrazku powyżej.

Timer/licznik może być taktowany wewnętrznie poprzez preskaler lub przez zewnętrzne źródło zegarowe na końcówce T0. Układ wyboru zegara określa, które źródło zegara oraz które zbocze impulsów zegarowych będzie używane przez timer/licznik do zwiększania (lub zmniejszania) jego wartości. Timer/licznik jest nieaktywny, jeśli nie zostało wybrane żadne źródło zegarowe. Wyjście z układu wyboru zegara jest określane jako zegar timera (ang. timer clock, clkT0). Podwójnie buforowane rejestry Output Compare (OCR0A i OCR0B) są przez cały czas porównywane z wartością timera/licznika. Wynik tych porównań może zostać użyty przez generator przebiegu, aby utworzyć przebieg PWM lub przebieg o zmiennej częstotliwości na końcówkach Output Compare (OC0A i OC0B). Szczegóły znajdziesz w podrozdziale "Moduł Output Compare”. Zdarzenie zgodności porównania ustawi również znacznik porównania (OCF0A lub OCF0B), który z kolei może zostać wykorzystany do generacji żądania przerwania Output Compare.

Wiele rejestrów i odwołań do bitów w tym rozdziale jest zapisanych w postaci ogólnej. Mała litera “n” zastępuje numer timera/licznika (w przypadku mikrokontrolerów AVR posiadających kilka takich modułów), w tym wypadku 0. Mała litera “x” zastępuje moduł Output Compare, w tym wypadku moduł porównania A (ang. Compare Unit A) lub moduł porównania B (ang. Compare Unit B). Jednakże w programie należy używać precyzyjnych nazw, np. TCNT0 przy dostępie do wartości timera/licznika0 itd.

Poniższe definicje są intensywnie używane w dalszej części tego rozdziału:

| Stała | Opis |

| BOTTOM | Licznik osiąga BOTTOM, gdy jego wartość staje się równa 0x00 |

| MAX | Licznik osiąga MAX, gdy jego wartość staje się równa 0xFF (dziesiętnie 255). |

| TOP | Licznik osiąga TOP, gdy jego wartość staje się równa największej wartości w sekwencji zliczania. Wartość TOP może być przypisana jako wartość stała 0xFF (MAX) lub wartość umieszczona w rejestrze OCR0A. Przypisanie to jest zależne od trybu pracy licznika. |

Timer/licznik może być taktowany bezpośrednio przez zegar systemowy (przez ustawienie CS[2:0] = 1). Udostępnia to najszybsze działanie z częstotliwością zegara timera/licznika równą częstotliwości zegara systemowego (fCLK_I/O). Alternatywnie można wykorzystać jedno z czterech wyjść preskalera jako źródło zegarowe. Daje to opcje częstotliwości zegara: fCLK_I/O / 8, fCLK_I/O / 64, fCLK_I/O / 256 lub fCLK_I/O / 1024.

Możliwe jest użycie resetu preskalera do synchronizacji timera/licznika z wykonywaniem programu.

Źródło zewnętrznego sygnału zegarowego przyłożonego do końcówki T0 może być używane jako zegar dla timera licznika (clkTn). Stan końcówki T0 jest próbkowany w każdym cyklu zegara systemowego przez układ logiczny synchronizacji końcówki. Zsynchronizowany (próbkowany) sygnał jest następnie przekazywany do detektora zbocza. Poniższy rysunek pokazuje schemat blokowy układu logicznego synchronizacji i detektora zbocza dla końcówki T0. Rejestry są taktowane przy zboczu dodatnim (0 → 1) wewnętrznego zegara systemowego (clkI/O). Przerzutnik latch jest przezroczysty w górnym okresie wewnętrznego zegara systemowego.

Detektor zbocza generuje jeden impls clkT0 dla każdego dodatniego (CSn2:0 = 7) lub ujemnego (CSn2:0 = 6) zbocza, które wykrywa.

Układ logiczny synchronizacji i detektora zbocza wprowadza opóźnienie od 2,5 do 3,5 cykli zegara systemowego od momentu pojawienia się zbocza na końcówce T0 do aktualizacji licznika. Włączanie i wyłączanie wejścia zegarowego musi być wykonywane, gdy T0 jest stabilne przynajmniej przez jeden cykl zegara systemowego, inaczej istnieje ryzyko generacji fałszywego impulsu zegarowego timera/licznika. Każdy półokres zewnętrznego zegara musi być dłuższy od jednego cyklu zegara systemowego, aby zapewnić poprawne próbkowanie. Należy zagwarantować, aby częstotliwość zegara zewnętrznego była mniejsza od połowy częstotliwości zegara systemowego (fExtClk < fclk_I/O / 2) przy wypełnieniu 50%/50%. Ponieważ detektor zbocza wykorzystuje próbkowanie, to maksymalna częstotliwość zegara zewnętrznego, który może poprawnie wykryć, wynosi połowę częstotliwości próbkowania (częstotliwość Nyquista). Jednakże z powodu wahań częstotliwości zegara systemowego oraz jego wypełnienia spowodowanych przez tolerancje oscylatora (kryształu, rezonatora i kondensatorów), zaleca się, aby maksymalna częstotliwość źródła zegara zewnętrznego była mniejsza od fclk_I/O / 2,5.

Źródło zegara zewnętrznego nie posiada preskalera.

Opis sygnałów (sygnały wewnętrzne):

| count | Zwiększenie lub zmniejszenie wartości TCNT0 o 1. | |

| direction | Wybór pomiędzy zmniejszaniem a zwiększaniem wartości licznika. | |

| clear | Zerowanie TCNT0 (ustawienie wszystkich bitów na 0). | |

| clkTn | Zegar timera/licznika. | |

| top | Sygnalizacja, iż licznik osiągnął wartość maksymalną. | |

| bottom | Sygnalizacja, iż licznik osiągnął wartość minimalną (zero). |

W zależności od użytego trybu działania licznik jest zerowany, zwiększany o 1 lub zmniejszany o 1 przy każdym takcie zegara timera (clkT0). Zegar clkT0 może być tworzony z zewnętrznego lub z wewnętrznego źródła, wybranego bitami wyboru zegara (ang. Clock Select bits, CS02:0). Gdy nie jest wybrane żadne źródło zegarowe (CS02:0 = 0), to timer jest zatrzymany. Jednakże zawartość TCNT0 jest dostępna dla mikroprocesora bez względu na obecność lub brak clkT0. Zapis przez mikroprocesor posiada wyższy priorytet nad wszystkimi operacjami zliczania lub zerowania.

Sekwencja zliczania jest określana przez ustawienia bitów WGM01 i WGM00 umieszczonych w rejestrze sterującym A timera/licznika (ang. Timer/Counter Control Register, TCCR0A) oraz bitu WGM02 umieszczonym w rejestrze sterującym B timera/licznika (ang. Timer/Counter Control Register B, TCCR0B). Istnieją bliskie związki pomiędzy sposobem zachowania się licznika (zliczaniem) a sposobem generacji przebiegów na wyjściu Output Compare, OC0A. Więcej na temat zaawansowanych sekwencji zliczania znajdziesz w podrozdziale "Tryby pracy".

Znacznik przepełnienia timera/licznika (ang. Timer/Counter Overflow Flag, TOV0) jest ustawiany zgodnie z trybem pracy wybranym przez bity WGM01:0. Znacznik TOV0 może być używany do generacji przerwania dla mikroprocesora.

Poniższy rysunek pokazuje schemat blokowy modułu Output Compare:

Rejestry OCR0x są podwójnie buforowane, gdy są używane tryby PWN (ang. Pulse Width Modulation). W trybie normalnym oraz w trybie zerowania timera przy zgodności porównania, CTC (ang. Clear Timer on Compare) podwójne buforowanie jest wyłączone. Synchronizuje ono uaktuaktualnianie rejestrów porównawczych OCR0x w czasie osiągnięcia wartości top lub bottom sekwencji zliczania. Synchronizacja zapobiega powstawaniu impulsów PWM o nieprawidłowej długości lub niesymetrycznych, co tworzy bezbłędne przebiegi wyjściowe.

Dostęp do rejestru OCR0x może wydawać się złożony, lecz tak nie jest. Gdy włączone jest podwójne buforowanie, mikroprocesor posiada dostęp do rejestru buforowego OCR0xr, a gdy buforowanie jest wyłączone, mikroprocesor ma bezpośredni dostęp do OCR0x.

W trybach nie generujących przebiegu PWM wyjście zgodności porównania z komparatora może zostać wymuszone przez zapis jedynki do bitu wymuszenia Output Compare (ang. Force Output Compare bit, 0x). Wymuszenie zgodności porównania nie ustawi znacznika OCF0x, ani nie wyzeruje/przeładuje timera, lecz końcówka OC0x zostanie uaktualniona tak, jakby wystąpiła rzeczywista zgodność porównania (ustawienie bitów COM01:0 definiuje, czy końcówka OC0x jest ustawiana, zerowana lub zmienia stan na przeciwny).

Wszystkie zapisy przez mikroprocesor do rejestru TCNT0 będą blokowały każdą zgodność porównania, która pojawi się w następnym cyklu zegara timera, nawet, jeśli timer został zatrzymany. Cecha ta pozwala zainicjować rejestr OCR0x na tę samą wartość co TCNT0 bez wyzwolenia przerwania, gdy zostanie włączony zegar timera/licznika.

Ponieważ zapis TCNT0 w dowolnym trybie pracy zablokuje wszystkie zgodności porównań na jeden cykl zegara timera, występuje ryzyko związane ze zmianą zawartości TCNT0, gdy jest używany moduł Output Compare niezależnie od tego, czy timer/licznik pracuje, czy nie. Jeśli wartość wpisana do TCNT0 jest równa wartości OCR0x, zgodność porównania zostanie przegapiona, co w wyniku da nieprawidłową generację przebiegu. Podobnie, nie wpisuj do TCNT0 wartości równej BOTTOM, gdy licznik zlicza w dół.

Ustawienie OC0x powinno być wykonane przed ustawieniem rejestru kierunku danych (ang. Data Direction Register) dla końcówki, która będzie wyjściem. Najprostszym sposobem ustawienia wartości OC0x jest użycie bitów strobowych wymuszonego Output Compare (FOC0x) w trybie normalnym. Rejestry OC0x utrzymują swoje wartości nawet przy zmianie trybów generacji przebiegów.

Bądź świadomy, iż bity COM0x1:0 nie są podwójnie buforowane wraz z wartością porównania. Zmiana bitów COM0x1:0 odniesie natychmiastowy skutek.

Bity trybu wyjścia porównania (ang. Compare Output Mode bits, COM0x1:0) posiadają dwie funkcje. Po pierwsze, generator przebiegu wykorzystuje bity COM0x1:0 do definiowania stanu końcówki wyjścia porównania (OC0x) przy kolejnej zgodności porównania. Po drugie, bity COM0x1:0 kontrolują źródło wyjściowe dla końcówki OC0x. Obrazek poniżej pokazuje uproszczony schemat sieci logicznej, na którą oddziałuje ustawienie bitów COM0x1:0. Rejestry we/wy, bity we/wy i końcówki we/wy na tym obrazku opisane są tłustym drukiem. Pokazane są tylko te elementy ogólnych rejestrów sterowania portami we/wy (DDR i PORT), na które wpływają bity COM0x1:0. Przy odwołaniu do stanu OC0x, odwołanie to dotyczy wewnętrznego rejestru OC0x, nie końcówki OC0x. Jeśli wystąpi reset, to rejestr OC0x zostanie wyzerowany.

Moduł wyjścia

zgodności porównania (ang. Compare Match

Output Unit) w trybie nie związanym z PWM

Ogólna funkcja portu we/we zostaje przejęta przez wyjście porównania (OC0x) z generatora przebiegu, jeśli dowolny z bitów COM0x1:0 jest ustawiony. Jednakże kierunek końcówki OC0x (wejście lub wyjście) jest wciąż kontrolowany przez rejestr kierunku danych (DDR) dla tej końcówki portu. Bit portu kierunku danych dla końcówki OC0x (DDR_OC0x) musi być ustawiony jako wyjście, zanim wartość OC0x stanie się widoczna na końcówce. Funkcja przejmowania jest niezależna od trybu pracy generatora przebiegu.

Zasada działania sieci logicznej dla końcówki Compare Output pozwala na inicjalizację stanu OC0x przed uaktywnieniem wyjścia. Zwróć uwagę, że niektóre z ustawień bitów COM0x1:0 są zarezerwowane tylko dla pewnych trybów pracy. Zobacz do podrozdziału "Opis Rejestrów".

Generator przebiegów używa bitów COM0x1:0 w różny sposób w trybach Normalnym, CTC i PWM. Dla wszystkich trybów ustawienie COM0x1:0 = 0 mówi generatorowi przebiegów, aby nie wykonywał żadnego działania na rejestrze OC0x przy następnej zgodności porównania. Opis funkcji tych bitów znajdziesz w opisie poszczególnych trybów.

Zmiana stanu bitów COM0x1:0 odnisie efekt przy pierwszej zgodności porównania, która wystąpi po tej zmianie. W trybach nie-PWM działanie może być wymuszone natychmiast przez wykorzystanie bitów strobowych FOC0x.

Najprostszym trybem pracy jest tryb normalny (ang. Normal Mode, WGM02:0 = 0). W tym trybie kierunek zliczania jest zawsze w górę (stan licznika sie zwiększa przy każdym impulsie zegarowym) i nie jest wykonywane żadne zerowanie licznika. Licznik po prostu się przewija, gdy osiąga swoją maksymalną wartość 8-bitową (MAX = 0xFF), a później startuje ponownie od wartości BOTTOM (0x00). W trybie normalnym znacznik przepełnienia timera/licznika (ang. Timer/Counter Overflow Flag, TOV0) zostanie ustawiony w tym samym cyklu zegarowym, gdy TCNT0 osiąga wartość zero. Znacznik TOV0 w tym przypadku zachowuje się jak 9-ty bit z tym wyjątkiem, że jest tylko ustawiany, nie zerowany. Jednakże w połączeniu z przerwaniem od przepełnienia timera (ang. timer overflow interrupt), które automatycznie zeruje znacznik TOV0, rozdzielczość timera może zostać zwiększona programowo. Nie ma specjalnych przypadków do rozważenia w trybie normalnym, nowa wartość dla licznika może zostać wpisana w dowolnym momencie.

W trybie normalnym używanie modułu Input Capture jest łatwe. Jednakże postaraj się przestrzegać, aby maksymalny interwał pomiędzy zdarzeniami zewnętrznymi nie przekraczał rozdzielczości licznika. Jeśli interwał pomiędzy dwoma zdarzeniami zewnętrznymi jest zbyt długi, musi zostać użyte przerwanie od przepełnienia timera lub preskaler, aby poszerzyć rozdzielczość modułu rejestracji zdarzeń.

Moduł Output Compare może być użyty do generowania przerwań w zadanych momentach czasu. Używanie Output Compare do generacji przebiegów w trybie normalnym nie jest zalecane, ponieważ zabiera to zbyt wiele czasu mikroprocesora.

W trybie zerowania timera przy zgodności porównania (ang. Clear Timer on Compare match, CTC) (WGM02:0 = 2), rejestr OCR0A jest używany do manipulowania rozdzielczością licznika. W trybie CTC licznik jest zerowany, gdy jego wartość (TCNT0) zrówna się z OCR0A. Rejestr OCR0A definiuje wartość szczytową dla licznika, a stąd również jego rozdzielczość. Ten tryb zapewnia większą kontrolę nad częstotliwością wyjścia zgodności porównania zgodności porównania. Upraszcza również operację zliczania zdarzeń zewnętrznych.

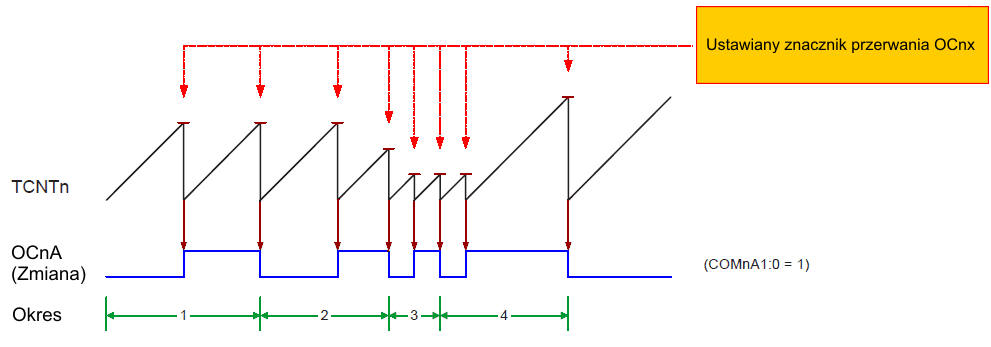

Wykres czasowy dla trybu CTC jest pokazany na poniższym rysunku. Wartość licznika (TCNT0) zwiększa się aż do pojawienia się zgodności porównania z OCR0A, a wtedy licznik (TCNT0) jest zerowany.

Przerwanie może zostać wygenerowane za każdym razem, gdy wartość licznika osiąga wartość TOP przy użyciu znacznika OCF0A. Jeśli to przerwanie jest uaktywnione, to procedura jego obsługi może zostać użyta do uaktualniania wartości TOP. Jednakże zmiana TOP na wartość bliską BOTTOM przy uruchomionym liczniku bez preskalera lub z małą wartością podziału preskalera musi być dokonywana ostrożnie, ponieważ tryb CTC nie posiada opcji podwójnego buforowania. Jeśli nowa wartość wpisana do OCR0A jest niższa od bieżącej wartości TCNT0, licznik przegapi zgodność porównania. W takim przypadku będzie on musiał zliczać do swojej wartości maksymalnej (0xFF) i rozpocząć od nowa zliczanie od 0x00, zanim będzie mogła wystąpić następna zgodność porównania. W wielu przypadkach taka cecha jest niepożądana.

Przy generowaniu przebiegu wyjściowego w trybie CTC wyjście OC0A może zostać ustawione na zmianę swojego poziomu logicznego przy każdej zgodności porównania przez ustawienie bitów trybu Compare Output na tryb zmiany (COM0A1:0 = 1). Wartość OC0A nie będzie widoczna na końcówce portu aż do ustawienia kierunku danych na wyjście (DDR_OC0A = 1). Generowany przebieg będzie posiadał maksymalną częstotliwość fOC0 = fclk_I/O/2, gdy OCR0A jest ustawione na zero (0x00). Częstotliwość przebiegu jest zdefiniowana wzorem:

Zmienna N reprezentuje współczynnik preskalera (1, 8, 64, 256 lub 1024).

Tak samo jak w trybie normalnym znacznik TOV0 jest ustawiany w tym samym cyklu zegara timera, gdy licznik zmienia stan z MAX na 0x00.

Szybki tryb PWM (ang. fast Pulse Width Modulation mode) (WGM02:0 = 3 lub 7) udostępnia opcję generowania przebiegu PWM o wysokiej częstotliwości. Szybkie PWM różni się od innych opcji PWM zliczaniem tylko w jednym kierunku. Licznik zlicza od BOTTOM do TOP, po czym znów rozpoczyna od BOTTOM. TOP jest zdefiniowane jako 0xFF, gdy WGM2:0 = 3, a jako OCRA, gdy WGM2:0 = 7. W trybie nieodwróconym Compare Output (ang. non-inverting Compare Output mode) wyjście Output Compare (OC0x) jest zerowane przy zgodności porównania pomiędzy TCNT0 a OCR0x i ustawiane przy BOTTOM. W trybie odwróconym Output Compare (ang. inverting Compare Output mode) wyjście jest ustawiane przy zgodności porównania i zerowane przy BOTTOM. Z powodu tego zliczania tylko w jednym kierunku, częstotliwość pracy szybkiego trybu PWM może być dwukrotnie wyższa niż w trybie PWM z poprawnością fazy, który wykorzystuje zliczanie dwukierunkowe. Ta wysoka częstotliwość sprawia, że szybki tryb PWM dobrze nadaje się do aplikacji sterujących mocą, stabilizacją oraz przetwarzaniem cyfrowo/analogowym. Wysoka częstotliwość umożliwia stosowanie mniejszych wymiarowo elementów zewnętrznych (cewek, kondensatorów), a przez to zmniejsza całkowity koszt systemu.

W szybkim trybie PWM licznik jest zwiększany co 1, aż jego zawartość osiągnie TOP. Licznik zostaje następnie wyzerowany przy następnym cyklu zegara timera. Na poniższym rysunku przedstawiono wykres czasowy dla szybkiego trybu PWM. Wartość TCNT0 jest na wykresie przedstawiona jako histogram dla zilustrowania jednokierunkowej operacji zliczania. Wykres zawiera wyjścia PWM nieodwrócone oraz odwrócone. Małe poziome odcinki na zboczach TCNT0 reprezentują zgodności porównań pomiędzy OCR0x a TCNT0.

Znacznik przepełnienia timera/licznika (ang. Timer/Counter Overflow Flag, TOV0) jest ustawiany zawsze, gdy licznik osiąga TOP. Jeśli przerwanie jest uaktywnione, to procedura jego obsługi może zostać użyta do uaktualniania wartości do porównań. W szybkim trybie PWM układ porównawczy pozwala na generację przebiegów PWM na końcówkach OC0x.

Ustawienie bitów COM0x1:0 na 2 utworzy nieodwrócony przebieg PWM, a odwrócony przebieg PWM może zostać wygenerowany przez ustawienie bitów COM0x1:0 na 3: ustawienie bitów COM0A1:0 na 1 umożliwia zmianę stanu końcówki OC0A przy zgodnościach porównań, jeśli jest ustawiony bit WGM02. Opcja ta jest niedostępna dla końcówki OC0B. Faktyczna wartość OC0x pojawi się na końcówce portu tylko wtedy, gdy końcówka ta zostanie ustawiona jako wyjście. Przebieg PWM jest generowany przez ustawianie (lub zerowanie) rejestru OC0x przy zgodności porównania pomiędzy OCR0x i TCNT0, a zerowanie (lub ustawianie) rejestru OC0x w cyklu zegara timera, w którym licznik jest zerowany (zmienia wartość z TOP na BOTTOM).

Częstotliwość przebiegu PWM na wyjściu może być obliczona z poniższego wzoru:

Zmienna N reprezentuje dzielnik preskalera (1, 8, 64, 256 lub 1024).

Wartości ekstremalne rejestru OCR0A reprezentują specjalne przypadki przy generacji przebiegu wyjściowego w szybkim trybie PWM. Jeśli OCR0A jest ustawiony na wartość równą BOTTOM, to na wyjściu pojawią się wąskie szpilki przy każdym MAX+1 cyklu zegara timera. Ustawienie OCR0A na wartość równą MAX spowoduje powstanie stałego przebiegu o wartości wysokiej lub niskiej (zależnie od polaryzacji wyjścia ustawianej bitami COM0x1:0).

Przebieg wyjściowy z wypełnieniem 50% w szybkim trybie PWM można osiągnąć przez ustawienie wyjścia OC0x na zmianę poziomu logicznego przy każdej zgodności porównania (COM0A1:0 = 1). Generowany przebieg będzie posiadał maksymalną częstotliwość fOC0 = fclk_I/O/2, gdy rejestr OCR0A zostanie ustawiony na zero. Ta cecha jest podobna do ustawienia zmiany poziomu OC0A w trybie CTC, z wyjątkiem tego, iż opcja podwójnego buforowania w module Output Compare jest uaktywniona w szybkim trybie PWM.

Tryb PWM poprawny fazowo (ang. phase correct PWM mode, WGM02:0 = 1 lub 5) udostępnia opcję generacji przebiegu PWM o wysokiej rozdzielczości i poprawnego fazowo. Oparty on jest na zliczaniu dwukierunkowym. Licznik w kółko zlicza od BOTTOM do TOP, a później od TOP do BOTTOM. TOP jest zdefiniowane jako 0xFF przy WGM2:0 = 1, a jako OCR0A przy WGM2:0 = 5. W nieodwróconym trybie Compare Output końcówka Output Compare (OC0x) jest ustawiana w stan niski przy zgodności porównania pomiędzy TCNT0 i OCR0x przy zliczaniu w górę, a ustawiana w stan wysoki przy tej zgodności porównania przy zliczaniu w dół. W odwróconym trybie Output Compare operacja jest odwrócona. Zliczanie dwukierunkowe skutkuje mniejszą częstotliwością pracy niż przy zliczaniu jednokierunkowym. Jednakże z powodu symetrii trybów PWM z dwukierunkowym zliczaniem są one preferowane w aplikacjach sterujących silnikami.

W trybie PWM poprawnym fazowo licznik jest zwiększany aż osiągnie wartość TOP. Gdy to się stanie, zmienia kierunek zliczania. Wartość TCNT0 będzie równa TOP przez jeden cykl zegara timera. Wykres czasowy trybu PWM poprawnego fazowo przedstawia rysunek poniżej. Wartość TCNT0 jest na wykresie pokazana jako histogram, aby zilustrować zliczanie w obu kierunkach. Wykres zawiera wyjścia PWM nieodwrócone i odwrócone. Małe, poziome linie na zboczach TCNT0 reprezentują zgodności porównań pomiędzy OCR0x a TCNT0.

Znacznik przepełnienia timera/licznika (ang. Timer/Counter Overflow Flag, TOV0) jest ustawiany za każdym razem, gdy licznik osiąga BOTTOM i może on zostać użyty do generowania przerwania w tym właśnie momencie.

W trybie PWM poprawnym fazowo moduł porównawczy pozwala generować przebiegi PWM na końcówkach OC0x. Ustawienie bitów COM0x1:0 na 2 wytworzy nieodwrócony przebieg PWM, a przebieg odwrócony powstanie przy ustawieniu COM0x1:0 na 3. Ustawienie bitów COM0A na 1 umożliwia zmianę stanu końcówki OC0A przy zgodności porównani, jeśli bit WGM02 został ustawiony. Opcja ta nie jest dostępna dla końcówki OC0B.

Faktyczna wartość OC0x pojawi się na końcówce portu tylko wtedy, gdy końcówka ta zostanie ustawiona jako wyjście. Przebieg PWM jest generowany przez zerowanie (lub ustawianie) rejestru OC0x przy zgodności porównania pomiędzy OCR0x i TCNT0, gdy licznik zlicza w górę, a ustawianie (lub zerowanie) rejestru OC0x przy zgodności porównania pomiędzy OCR0x a TCNT0, gdy licznik zlicza w dół. Wyjściową częstotliwość PWM w trybie PWM poprawnym fazowo obliczamy wg poniższego wzoru:

Zmienna N reprezentuje dzielnik preskalera (1, 8, 64, 256 lub 1024).

Wartości ekstremalne dla rejestru OCR0A reprezentują specjalne przypadki przy generacji przebiegu PWM w trybie poprawnym fazowo. Jeśli OCR0A zostanie ustawiony na BOTTOM, to wyjście będzie stale w stanie niskim, a jeśli ustawi się go na MAX, to na wyjściu ciągle będzie stan wysoki w trybie nieodwróconym PWM. W trybie odwróconym PWM wyjście będzie w przeciwnych stanach logicznych.

Na samym początku okresu 2 na wykresie powyżej OCn przechodzi ze stanu wysokiego w niski, nawet jeśli nie występuje zgodność porównania. Miejsce tego przejścia ma zagwarantować symetryczność wokół BOTTOM. Istnieją dwa przypadki dające takie przejście bez zgodności porównania.

Wykres czasowy Timera/Licznika bez

preskalera

Następny wykres pokazuje te same dane, lecz z uruchomionym preskalerem (fclk_I/O:8):

Kolejny wykres pokazuje ustawianie znacznika OCF0B we wszystkich trybach oraz znacznika OCF0A we wszystkich trybach z wyjątkiem trybów CTC i PWM, gdzie OCR0A ma wartość TOP:

Kolejny wykres pokazuje ustawianie znacznika OCF0A i zerowanie licznika TCNT0 w trybach CTC i szybkim PWM, gdzie OCR0A ma wartość TOP.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x2C | TSM | PWM1B | COM1B1 | COM1B0 | FOC1B | FOC1A | PSR1 | PSR0 | GTCCR |

| Zapis/Odczyt | Z/O | O | O | O | O | O | O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Zapis logicznej jedynki do bitu TSM aktywuje tryb synchronizacji timera/licznika. W trybie tym wartość wpisana do bitu PSR zostaje utrzymana, co daje ciągły sygnał resetu preskalera. Zapewnia to, iż timer/licznik zostaje zatrzymany i można go skonfigurować bez ryzyka zwiększania jego zawartości podczas konfiguracji. Gdy bit TSM zostaje zapisany stanem logicznym zera, bit PSR jest zerowany sprzętowo i timer/licznik rozpoczyna zliczanie.

Gdy ten bit ma wartość jeden, resetowany jest preskaler timera/licznika 0. Ten bit normalnie zostaje natychmiast wyzerowany sprzętowo z wyjątkiem przypadku, gdy bit TSM jest ustawiony na 1.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x2A | COM0A1 | COM0A0 | COM0B1 | COM0B0 | - | - | WGM01 | WGM00 | TCCR0A |

| Zapis/Odczyt | Z/O | Z/O | Z/O | Z/O | O | O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bity te sterują zachowaniem końcówki Output Compare A (OC0A). Jeśli jeden lub oba bity COM0A1:0 są ustawione, to wyjście OC0A przejmuje normalną funkcję portu końcówki we/wy. Jednakże zauważ, iż bit rejestru kierunku danych (ang. Data Direction Register, DDR) odpowiadający końcówce OC0A musi być ustawiony w celu uaktywnienia jej jako wyjście.

Gdy wyjście OC0A jest połączone z końcówką, funkcje bitów COM0A1:0 zależą od ustawienia bitów WGM02:0.

Funkcje bitów COM0A1:0, gdy bity WGM02:0 są ustawione na tryb normalny lub CTC (nie PWM):

| COM0A1 | COM0A0 | Opis |

| 0 | 0 | Normalna praca portu, OC0A odłączone. |

| 0 | 1 | Zmiana wartości OC0A na przeciwną przy zgodności porównania. |

| 1 | 0 | Zerowanie OC0A przy zgodności porównania. |

| 1 | 1 | Ustawienie OC0A przy zgodności porównania. |

Funkcje bitów COM0A1:0, gdy bity WGM02:0 są ustawione na szybki tryb PWM:

| COM0A1 | COM0A0 | Opis |

| 0 | 0 | Normalna praca portu, OC0A odłączone. |

| 0 | 1 | WGM02 = 0: Normalna

praca portu, OC0A odłączone. WGM02 = 1: Zmiana wartości OC0A na przeciwną przy zgodności porównania. |

| 1 | 0 | Zerowanie OC0A przy zgodności porównania, ustawienie OC0A przy TOP. |

| 1 | 1 | Ustawienie OC0A przy zgodności porównania, zerowanie OC0A przy TOP. |

| Uwaga: | 1. | Specjalny przypadek występuje, gdy rejestr OCR0A ma zawartość równą TOP, a bit COM0A1 jest ustawiony. W takim przypadku zgodność porównania jest ignorowana, lecz ustawianie lub zerowanie jest wykonywane przy wartości TOP. Zobacz do podrozdziału "Szybki tryb PWM". |

Funkcje bitów COM0A1:0, gdy bity WGM02:0 są ustawione na tryb PWM poprawny fazowo:

| COM0A1 | COM0A0 | Opis |

| 0 | 0 | Normalna praca portu, OC0A odłączone. |

| 0 | 1 | WGM02 = 0: Normalna

praca portu, OC0A odłączone. WGM02 = 1: Zmiana wartości OC0A na przeciwną przy zgodności porównania. |

| 1 | 0 | Zerowanie OC0A przy

zgodności porównania przy zliczaniu w górę. Ustawienie OC0A przy zgodności porównania przy zliczaniu w dół. |

| 1 | 1 | Ustawienie OC0A przy

zgodności porównania przy zliczaniu w górę. Zerowanie OC0A przy zgodności porównania przy zliczaniu w dół. |

| Uwaga: | 1. | Specjalny przypadek występuje, gdy rejestr OCR0A ma zawartość równą TOP, a bit COM0A1 jest ustawiony. W takim przypadku zgodność porównania jest ignorowana, lecz ustawianie lub zerowanie jest wykonywane przy wartości TOP. Zobacz do podrozdziału "Tryb PWM poprawny fazowo". |

Te bity sterują zachowaniem końcówki Output Compare B (OC0B).Jeśli jeden lub oba bity COM0B1:0 są ustawione, to wyjście OC0B przejmuje normalną funkcję portu końcówki we/wy. Jednakże zauważ, iż bit rejestru kierunku danych (ang. Data Direction Register, DDR) odpowiadający końcówce OC0B musi być ustawiony w celu uaktywnienia jej jako wyjście.

Gdy wyjście OC0B jest połączone z końcówką, funkcje bitów COM0B1:0 zależą od ustawienia bitów WGM02:0.

Funkcje bitów COM0B1:0, gdy bity WGM02:0 są ustawione na tryb normalny lub CTC (nie PWM):

| COM0B1 | COM0B0 | Opis |

| 0 | 0 | Normalna praca portu, OC0B odłączone. |

| 0 | 1 | Zmiana wartości OC0B na przeciwną przy zgodności porównania. |

| 1 | 0 | Zerowanie OC0B przy zgodności porównania. |

| 1 | 1 | Ustawienie OC0B przy zgodności porównania. |

Funkcje bitów COM0B1:0, gdy bity WGM02:0 są ustawione na szybki tryb PWM:

| COM0B1 | COM0B0 | Opis |

| 0 | 0 | Normalna praca portu, OC0B odłączone. |

| 0 | 1 | Zarezerwowane |

| 1 | 0 | Zerowanie OC0B przy zgodności porównania, ustawienie OC0B przy TOP. |

| 1 | 1 | Ustawienie OC0B przy zgodności porównania, zerowanie OC0B przy TOP. |

| Uwaga: | 1. | Specjalny przypadek występuje, gdy rejestr OCR0B ma zawartość równą TOP, a bit COM0B1 jest ustawiony. W takim przypadku zgodność porównania jest ignorowana, lecz ustawianie lub zerowanie jest wykonywane przy wartości TOP. Zobacz do podrozdziału "Szybki tryb PWM". |

Funkcje bitów COM0B1:0, gdy bity WGM02:0 są ustawione na tryb PWM poprawny fazowo:

| COM0B1 | COM0B0 | Opis |

| 0 | 0 | Normalna praca portu, OC0A odłączone. |

| 0 | 1 | Zarezerwowane |

| 1 | 0 | Zerowanie OC0B przy

zgodności porównania przy zliczaniu w górę. Ustawienie OC0B przy zgodności porównania przy zliczaniu w dół. |

| 1 | 1 | Ustawienie OC0B przy

zgodności porównania przy zliczaniu w górę. Zerowanie OC0B przy zgodności porównania przy zliczaniu w dół. |

| Uwaga: | 1. | Specjalny przypadek występuje, gdy rejestr OCR0B ma zawartość równą TOP, a bit COM0B1 jest ustawiony. W takim przypadku zgodność porównania jest ignorowana, lecz ustawianie lub zerowanie jest wykonywane przy wartości TOP. Zobacz do podrozdziału "Tryb PWM poprawny fazowo". |

Bity te są w ATtiny25/45/85 zarezerwowane i przy odczycie dają zawsze wartość 0.

Bity te w połączeniu z bitem WGM02 znajdującym się w rejestrze TCCR0B sterują sposobem zliczania przez licznik, źródłem wartości maksymalnej (TOP) oraz typem generacji przebiegu, który ma zostać użyty. Moduł timera/licznika wspiera następujące tryby pracy: tryb normalny (licznik), tryb zerowania licznika przy zgodności porównania (ang. Clear Timer on Compare Match, CTC) oraz dwa tryby modulacji szerokości impulsu (ang. Pulse Width Modulation, PWM). Zobacz do podrozdziału "Tryby pracy".

Funkcje bitów trybu generacji przebiegu

| Nr trybu | WGM2 | WGM1 | WGM0 | Tryb pracy modułu | TOP | Zmiana OCRx przy | Ustawianie TOV przy(1)(2) |

| 0 | 0 | 0 | 0 | Normalny | 0xFF | Natychmiast | MAX |

| 1 | 0 | 0 | 1 | PWM (poprawny fazowo) | 0xFF | TOP | BOTTOM |

| 2 | 0 | 1 | 0 | CTC | OCRA | Natychmiast | MAX |

| 3 | 0 | 1 | 1 | szybki PWM | 0xFF | BOTTOM | MAX |

| 4 | 1 | 0 | 0 | Zarezerwowane | – | – | – |

| 5 | 1 | 0 | 1 | PWM (poprawny fazowo) | OCRA | TOP | BOTTOM |

| 6 | 1 | 1 | 0 | Zarezerwowane | – | – | – |

| 7 | 1 | 1 | 1 | szybki PWM | OCRA | BOTTOM | TOP |

| Uwaga: | 1. | MAX = 0xFF |

| 2. | BOTTOM = 0x00 |

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x33 | FOC0A | FOC0B | - | - | WGM02 | CS02 | CS01 | CS00 | TCCR0B |

| Zapis/Odczyt | Z | Z | O | O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bit FOC0A jest aktywny tylko wtedy, gdy bity WGM2:0 określają tryb nie-PWM.

Jednakże dla kompatybilności z przyszłymi urządzeniami bit ten musi być zapisywany zerem przy zapisie do rejestru TCCR0B w czasie pracy w trybie PWM. Gdy do bitu FOC0A zostanie zapisana logiczna jedynka, zostaje natychmiast wymuszona zgodność porównania na module generacji przebiegu. Wyjście OC0A jest zmieniane zgodnie z ustawieniami bitów COM0A1:0. Zwróć uwagę, iż bit FOC0A jest zaimplementowany jako strob. Dlatego to wartość obecna w bitach COM0A1:0 określa efekt wymuszonej zgodności porównania.

Strob FOC0A nie wygeneruje żadnego przerwania, ani nie wyzeruje timera w trybie CTC używającego rejestru OCR0A jako TOP.

Przy odczycie bit FOC0A daje zawsze wartość zero.

Bit FOC0B jest aktywny tylko wtedy, gdy bity WGM2:0 określają tryb nie-PWM.

Jednakże dla kompatybilności z przyszłymi urządzeniami bit ten musi być zapisywany zerem przy zapisie do rejestru TCCR0B w czasie pracy w trybie PWM. Gdy do bitu FOC0B zostanie zapisana logiczna jedynka, zostaje natychmiast wymuszona zgodność porównania na module generacji przebiegu. Wyjście OC0B jest zmieniane zgodnie z ustawieniami bitów COM0B1:0. Zwróć uwagę, iż bit FOC0B jest zaimplementowany jako strob. Dlatego to wartość obecna w bitach COM0B1:0 określa efekt wymuszonej zgodności porównania

Strob FOC0B nie wygeneruje żadnego przerwania, ani nie wyzeruje timera w trybie CTC używającego rejestru OCR0B jako TOP.

Przy odczycie bit FOC0B daje zawsze wartość zero.

Bity te są w ATtiny25/45/85 zarezerwowane i przy odczycie dają zawsze wartość 0.

Zobacz do opisu rejestru TCCR0A.

Trzy bity wyboru zegara wybierają źródło zegarowe, z którego będzie korzystał timer/licznik.

| CS02 | CS01 | CS00 | Opis |

| 0 | 0 | 0 | Brak źródła zegarowego (timer/licznik zatrzymany) |

| 0 | 0 | 1 | clkI/O/1 (bez preskalera) |

| 0 | 1 | 0 | clkI/O/8 (z preskalera) |

| 0 | 1 | 1 | clkI/O/64 (z preskalera) |

| 1 | 0 | 0 | clkI/O/256 (z preskalera) |

| 1 | 0 | 1 | clkI/O/1024 (z preskalera) |

| 1 | 1 | 0 | Zewnętrzne źródło zegarowe na końcówce T0. Aktywne zbocze opadające. |

| 1 | 1 | 1 | Zewnętrzne źródło zegarowe na końcówce T0. Aktywne zbocze narastające. |

Jeśli zostanie wybrane zewnętrzne źródło zegarowe dla timera/licznika 0, zmiany poziomu logicznego na końcówce T0 będą taktowały licznika nawet wtedy, gdy końcówka zostanie skonfigurowana jako wyjście. Cecha ta pozwala na programowe sterowanie zliczaniem.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x32 | TCNT0[7:0] | TCNT0 | |||||||

| Zapis/Odczyt | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

Rejestr timera/licznika daje bezpośredni dostęp zarówno przy odczycie jak i przy zapisie do zawartości 8-bitowego licznika w module timera/licznika. Zapis do rejestru TCNT0 blokuje (usuwa) zgodność porównania przy następnym cyklu zegara timera. Modyfikowanie licznika (TCNT0) podczas jego pracy wprowadza ryzyko pominięcia zgodności porównania pomiędzy TCNT0 a rejestrami OCR0x.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x29 | OCR0A[7:0] | OCR0A | |||||||

| Zapis/Odczyt | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

Rejestr A dla Output Compare zawiera 8-bitową wartość, która jest ciągle porównywana z zawartością licznika (TCNT0). Zgodność może zostać wykorzystana do generacji przerwania Output Compare lub do generacji przebiegu wyjściowego na końcówce OC0A.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x28 | OCR0B[7:0] | OCR0B | |||||||

| Zapis/Odczyt | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

Rejestr B dla Output Compare zawiera 8-bitową wartość, która jest ciągle porównywana z zawartością licznika (TCNT0). Zgodność może zostać wykorzystana do generacji przerwania Output Compare lub do generacji przebiegu wyjściowego na końcówce OC0B.

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x39 | – | OCIE1A | OCIE1B | OCIE0A | OCIE0B | TOIE1 | TOIE0 | – | TIMSK |

| Zapis/Odczyt | O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bity te są w ATtiny25/45/85 zarezerwowane i przy odczycie daje zawsze wartość 0.

Gdy bit OCIE0A zostanie ustawiony na jeden, a bit I w rejestrze stanu jest również ustawiony, to jest uaktywniane przerwanie przy zgodności porównania A w timerze/liczniku. Przerwanie to jest wykonywane, jeśli w timerze/liczniku wystąpi zgodność porównania, tj. gdy zostanie ustawiony bit OCF0A w rejestrze znaczników przerwań od timera/licznika (ang. Timer/Counter Interrupt Flag Register, TIFR).

Gdy bit OCIE0B zostanie ustawiony na jeden, a bit I w rejestrze stanu jest również ustawiony, to jest uaktywniane przerwanie przy zgodności porównania B w timerze/liczniku. Przerwanie to jest wykonywane, jeśli w timerze/liczniku wystąpi zgodność porównania, tj. gdy zostanie ustawiony bit OCF0B bit w rejestrze znaczników przerwań od timera/licznika (ang. Timer/Counter Interrupt Flag Register, TIFR).

Gdy bit TOIE0 zostanie zapisany stanem jeden, a bit I w rejestrze stanu jest ustawiony, to jest uaktywniane przerwanie przy przepełnieniu timera/licznika 0. Przerwanie to jest wykonywane, jeśli wystąpi przepełnienie w timerze/liczniku 0, tj. gdy zostanie ustawiony bit TOV0 w rejestrze znaczników przerwań od timera/licznika (ang. Timer/Counter Interrupt Flag Register, TIFR).

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x38 | – | OCF1A | OCF1B | OCF0A | OCF0B | TOV1 | TOV0 | – | TIFR |

| Zapis/Odczyt | O | Z/O | Z/O | Z/O | Z/O | Z/O | Z/O | O | |

| Wartość początkowa | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Bity te są w ATtiny25/45/85 zarezerwowane i przy odczycie daje zawsze wartość 0.

Bit OCF0A jest ustawiany, gdy wystąpi zgodność porównania pomiędzy timerem/licznikiem 0 a danymi w rejestrze Output Compare 0 A (ang. Output Compare Register0 A, OCR0A). Bit OCF0A jest zerowany sprzętowo przy wykonaniu odpowiedniego wektora przerwania. Alternatywnie można go wyzerować przez zapis do znacznika logicznej jedynki. Gdy są ustawione bity: I w SREG, OCIE0AB i OCF0A, zostaje wykonane przerwanie przy zgodności porównania.

Bit OCF0B jest ustawiany, gdy wystąpi zgodność porównania pomiędzy timerem/licznikiem 0 a danymi w rejestrze Output Compare 0 B (ang. Output Compare Register0 B, OCR0B). Bit OCF0B jest zerowany sprzętowo przy wykonaniu odpowiedniego wektora przerwania. Alternatywnie można go wyzerować przez zapis do znacznika logicznej jedynki. Gdy są ustawione bity: I w SREG, OCIE0B i OCF0B, zostaje wykonane przerwanie przy zgodności porównania.

Bit TOV0 jest ustawiany, gdy wystąpi przepełnienie w timerze/liczniku 0. Bit TOV0 jest zerowany sprzętowo przy wykonaniu odpowiedniego wektora przerwania. Alternatywnie można go wyzerować przez zapis do znacznika logicznej jedynki. Gdy są ustawione bity I w SREG oraz TOV0, zostaje wykonane przerwanie od przepełnienia timera/licznika 0.

Ustawianie tego znacznika zależy od ustawienia bitów WGM02:0:

| Nr trybu | WGM2 | WGM1 | WGM0 | Tryb pracy modułu | TOP | Zmiana OCRx przy | Ustawianie TOV przy(1)(2) |

| 0 | 0 | 0 | 0 | Normalny | 0xFF | Natychmiast | MAX |

| 1 | 0 | 0 | 1 | PWM (poprawny fazowo) | 0xFF | TOP | BOTTOM |

| 2 | 0 | 1 | 0 | CTC | OCRA | Natychmiast | MAX |

| 3 | 0 | 1 | 1 | szybki PWM | 0xFF | BOTTOM | MAX |

| 4 | 1 | 0 | 0 | Zarezerwowane | – | – | – |

| 5 | 1 | 0 | 1 | PWM (poprawny fazowo) | OCRA | TOP | BOTTOM |

| 6 | 1 | 1 | 0 | Zarezerwowane | – | – | – |

| 7 | 1 | 1 | 1 | szybki PWM | OCRA | BOTTOM | TOP |

| Uwaga: | 1. | MAX = 0xFF |

| 2. | BOTTOM = 0x00 |

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.