|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

|

Wyjście Spis treści Wstecz Dalej

Autor artykułu |

©2026 mgr Jerzy Wałaszek

|

If you use Microchip copyrighted material solely for educational (non-profit) purposes falling under the “fair use” exception of the U.S. Copyright Act of 1976 then you do not need Microchip’s written permission. For example, Microchip’s permission is not required when using copyrighted material in: (1) an academic report, thesis, or dissertation; (2) classroom handouts or textbook; or (3) a presentation or article that is solely educational in nature (e.g., technical article published in a magazine).

https://www.microchip.com/about-us/legal-information/copyright-usage-guidelines

| Bit blokujący | Numer bitu | Opis | Wartość standardowa(1) |

| 7 | – | 1 (niezaprogramowany) | |

| 6 | – | 1 (niezaprogramowany) | |

| 5 | – | 1 (niezaprogramowany) | |

| 4 | – | 1 (niezaprogramowany) | |

| 3 | – | 1 (niezaprogramowany) | |

| 2 | – | 1 (niezaprogramowany) | |

| LB2 | 1 | Bit blokujący | 1 (niezaprogramowany) |

| LB1 | 0 | Bit blokujący | 1 (niezaprogramowany) |

Uwaga: 1. "1" oznacza stan niezaprogramowany, "0" oznacza stan zaprogramowany.

Tryby zabezpieczeń bitów blokujących

| Bity blokowania pamięci(1)(2) | Rodzaj zabezpieczenia | ||

| Tryb LB | LB2 | LB1 | |

| 1 | 1 | 1 | Brak funkcji pamięci blokowania. |

| 2 | 1 | 0 | Dalsze programowanie pamięci FLASH i EEPROM jest zablokowane w trybach programowania wysokonapięciowego oraz szeregowego. Bity bezpiecznikowe zostają zablokowane w trybach programowania wysokonapięciowego i szeregowego. Interfejs debugWire jest zablokowany. |

| 3 | 0 | 0 | Dalsze programowanie i

weryfikacja pamięci FLASH i EEPROM są zablokowane w

trybach programowania wysokonapięciowego oraz

szeregowego. Bity bezpiecznikowe zostają zablokowane w trybach programowania wysokonapięciowego i szeregowego(1). Interfejs debugWire jest zablokowany. |

| Uwagi: | 1. | Zaprogramuj bity bezpiecznikowe przed bitami blokującymi. |

| 2. | "1" oznacza stan niezaprogramowany, "0" oznacza stan zaprogramowany. |

Rozszerzony bajt bitów bezpiecznikowych

| Bit bezpiecznikowy | Numer bitu | Opis | Wartość standardowa |

| – | 7 | – | 1 (niezaprogramowane) |

| – | 6 | – | 1 (niezaprogramowane) |

| – | 5 | – | 1 (niezaprogramowane) |

| – | 4 | – | 1 (niezaprogramowane) |

| – | 3 | – | 1 (niezaprogramowane) |

| – | 2 | – | 1 (niezaprogramowane) |

| – | 1 | – | 1 (niezaprogramowane) |

| SELFPRGEN(1) | 0 | Uaktywnienie samoprogramowania | 1 (niezaprogramowane) |

| Uwagi: | 1. | Uaktywnia instrukcję SPM. Zobacz do rozdziału "Samoprogramowanie FLASH" |

Górny bajt bitów bezpiecznikowych

| Bit bezpiecznikowy | Numer bitu | Opis | Wartość standardowa |

| RSTDISBL (1) | 7 | Zablokowanie zewnętrznego resetu | 1 (niezaprogramowane) |

| DWEN (2) | 6 | Uaktywnienie DebugWIRE | 1 (niezaprogramowane) |

| SPIEN (3) | 5 | Uaktywnienie programowania szeregowego i ładowania danych | 0 (zaprogramowane) |

| WDTON (4) | 4 | Licznik zegarowy zawsze włączony | 1 (niezaprogramowane) |

| EESAVE | 3 | Zachowanie zawartości EEPROM przy kasowaniu układu | 1 (niezaprogramowane) |

| BODLEVEL2 (5) | 2 | Poziom wyzwalania w detektorze spadku napięcia zasilającego | 1 (niezaprogramowane) |

| BODLEVEL1 (5) | 1 | Poziom wyzwalania w detektorze spadku napięcia zasilającego | 1 (niezaprogramowane) |

| BODLEVEL0 (5) | 0 | Poziom wyzwalania w detektorze spadku napięcia zasilającego | 1 (niezaprogramowane) |

| Uwagi: | 1. | Zobacz do podrozdziału "Alternatywne funkcje portów", gdzie opisano funkcje bitów bezpiecznikowych RSTDISBL i DWEN. Po zaprogramowaniu bitu bezpiecznikowego RSTDISBL do zmiany bitów bezpiecznikowych i w celu dalszego programowania mikrokontrolera niezbędne jest użycie wysokonapięciowego programowania szeregowego. |

| 2. | DWEN nie może być zaprogramowany gdy są wymagane zabezpieczenia bitami blokującymi. Zobacz do podrozdziału "Bity blokujące pamięci programu i danych". | |

| 3. | Bit bezpiecznikowy SPIEN nie jest dostępny w trybie programowania SPI. | |

| 4. | Zaprogramowanie tego bitu wyłączy przerwanie od licznika zegarowego. | |

| 5. | Zobacz do rozdziału "Parametry elektryczne". |

Dolny bajt bitów bezpiecznikowych

| Bit bezpiecznikowy | Numer bitu | Opis | Wartość standardowa |

| CKDIV8 (1) | 7 | Podział zegara przez 8 | 0 (zaprogramowane) |

| CKOUT (2) | 6 | Włączenie wyjścia zegarowego | 1 (niezaprogramowane) |

| SUT1 (3) | 5 | Wybór czasu uruchamiania | 1 (niezaprogramowane) |

| SUT0 (3) | 4 | Wybór czasu uruchamiania | 0 (zaprogramowane) |

| CKSEL3 (4) | 3 | Wybór źródła zegarowego | 0 (zaprogramowane) |

| CKSEL2 (4) | 2 | Wybór źródła zegarowego | 0 (zaprogramowane) |

| CKSEL1 (4) | 1 | Wybór źródła zegarowego | 1 (niezaprogramowane) |

| CKSEL0 (4) | 0 | Wybór źródła zegarowego | 0 (zaprogramowane) |

| Uwagi: | 1. | Szczegóły znajdziesz w rozdziale "System zegarowy". |

| 2. | Pozwala wyprowadzać zegar systemowy na końcówce zewnętrznej CKOUT. | |

| 3. | Standardowy wybór daje w wyniku maksymalny czas uruchamiania przy standardowym źródle zegarowym. | |

| 4. | Standardowym wyborem jest wewnętrzny oscylator RC przy częstotliwości 8,0 MHz. |

Zauważ, iż bity bezpiecznikowe zostają zablokowane, jeśli bit blokujący LB1 jest zaprogramowany. Programuj bity bezpiecznikowe przed bitami blokującymi. Stan bitów bezpiecznikowych nie jest zmieniany przez kasowanie zawartości układu (ang. Chip Erase).

Bity bezpiecznikowe można odczytać również z poziomu oprogramowania. Zobacz do podrozdziału "Programowy odczyt bitów bezpiecznikowych i blokujących".

Wartości bitów bezpiecznikowych są zatrzaskiwane, gdy mikrokontroler wchodzi w tryb programowania, a zmiany ich stanów nie będą obowiązywały aż do wyjścia z trybu programowania. Nie odnosi się to do bitu bezpiecznikowego EESAVE, który funkcjonuje natychmiast po zaprogramowaniu. Bity bezpiecznikowe są również zatrzaskiwane przy uruchamianiu w trybie normalnym.

Zawartość tablicy sygnaturowej

| Adres | Górny bajt |

| 0x00 | Bajt sygnaturowy 0 |

| 0x01 | Dane kalibracyjne dla wewnętrznego oscylatora (2) |

| 0x02 | Bajt sygnaturowy 1 |

| 0x03 | Zarezerwowane na wewnętrzny użytek |

| 0x04 | Bajt sygnaturowy 2 |

| 0x05...0x2A | Zarezerwowane na wewnętrzny użytek |

Wszystkie mikrokontrolery Atmel posiadają trzy-bajtowy kod sygnatury, który je identyfikuje. Kod ten można odczytać w trybie programowania szeregowego i w trybie programowania wysokonapięciowego, nawet gdy mikrokontroler został zablokowany bitami blokującymi.

Bajty sygnatury można również odczytać programowo, zobacz do podrozdziału "Programowy odczyt bitów bezpiecznikowych i blokujących".

Te trzy bajty sygnaturowe przebywają w oddzielnej przestrzeni adresowej zwanej tablicą sygnaturową mikrokontrolera (ang. device signature imprint table). Poniższa tabelka podaje bajty sygnaturowe dla ATtiny25/45/85:

| Mikrokontroler | Bajt 0 | Bajt 1 | Bajt 1 |

| ATtiny25 | 0x1E | 0x91 | 0x08 |

| ATtiny45 | 0x1E | 0x92 | 0x06 |

| ATtiny85 | 0x1E | 0x93 | 0x0B |

Tablica sygnaturowa mikrokontrolera ATtiny25/45/85 zawiera dwa bajty danych kalibracyjnych dla wewnętrznego oscylatora RC. W normalnym trybie pracy dane kalibracyjne dla częstotliwości roboczej 8 MHz są automatycznie pobierane i zapisywane do rejestru OSCCAL podczas resetu. W trybie kompatybilności z ATtiny15 używane są zastępczo dane dla częstotliwości roboczej 6,4 MHz. Ta procedura daje gwarancję, iż wewnętrzny oscylator zostanie zawsze skalibrowany na poprawną częstotliwość pracy. Bajty kalibracyjne można również odczytywać programowo. Zobacz do podrozdziału "Programowy odczyt bitów bezpiecznikowych i blokujących".

Liczba słów na stronę oraz liczba stron pamięci FLASH

| Mikrokontroler | Rozmiar FLASH | Rozmiar strony | PCWORD | Liczba stron | PCPAGE | PCMSB |

| ATtiny25 | 1K słów (2 KB) |

16 słów | PC[3:0] | 64 | PC[9:4] | 9 |

| ATtiny45 | 2K słów (4 KB) |

32 słowa | PC[4:0] | 64 | PC[10:5] | 10 |

| ATtiny85 | 4K słów (8 KB) |

32 słowa | PC[4:0] | 128 | PC[11:5] | 11 |

| PC | – | bity adresu słowa w pamięci programu |

| PCWORD | – | bity adresu słowa na stronie FLASH |

| PCPAGE | – | bity adresu strony FLASH |

| PCMSB | – | numer najstarszego bitu w adresie |

Liczba słów na stronę oraz liczba stron pamięci EEPROM

| Mikrokontroler | Rozmiar EEPROM | Rozmiar strony | EEAWORD | Liczba stron | EEAPAGE | EEAMSB |

| ATtiny25 | 128 B | 4 bajty | EEA[1:0] | 32 | EEA[6:2] | 6 |

| ATtiny45 | 256 B | 4 bajty | EEA[1:0] | 64 | EEA[7:2] | 7 |

| ATtiny85 | 512 B | 4 bajty | EEA[1:0] | 128 | EEA[8:2] | 8 |

| EEA | – | bity adresu bajtu w pamięci EEPROM |

| EEAWORD | – | bity adresu bajtu na stronie EEPROM |

| EEAPAGE | – | bity adresu strony EEPROM |

| EEAMSB | – | numer najstarszego bitu w adresie |

Interfejs szeregowy składa się z końcówek SCK (zegar), MOSI (wejście) i MISO (wyjście).

Uwaga: Jeśli mikrokontroler jest taktowany przez wewnętrzny oscylator, to nie ma potrzeby dołączania do niego źródła zegarowego przez końcówkę CLKI.

Po ustawieniu RESET w stan niski, należy wysłać do mikrokontrolera instrukcję włączającą programowanie zanim operacje programowania/wymazywania będą mogły być wykonywane.

Odwzorowanie końcówek przy programowaniu szeregowym

| Symbol | Końcówki | we/wy | Opis |

| MOSI | PB0 | we | Wejście danych szeregowych |

| MISO | PB1 | wy | Wyjście danych szeregowych |

| SCK | PB2 | we | Wejście zegara szeregowego |

Przy programowaniu EEPROM w operacji programowania wbudowany jest cykl samokasowania (TYLKO w trybie szeregowym) i nie ma potrzeby wcześniejszego wykonywania instrukcji kasowania układu (ang. Chip Erase instruction). Operacja kasowania układu zamienia zawartość każdej komórki w obu pamięciach programu i EEPROM w 0xFF.

W zależności od bitów bezpiecznikowych CKSEL musi być obecny poprawny sygnał zegarowy. Minimalne okresy stanu niskiego i wysokiego dla wejścia zegara szeregowego (SCK) są zdefiniowane następująco:

Gdy dane szeregowe są zapisywane do ATtiny25/45/85, ich odczyt przez mikroprocesor następuje na narastającym zboczu sygnału zegarowego SCK. Gdy dane są odczytywane z ATtiny25/45/85, ich próbkowanie następuje przy opadającym zboczu sygnału SCK.

Aby zaprogramować i zweryfikować mikrokontroler ATtiny25/45/85 w trybie programowania szeregowego, zaleca się następujący ciąg operacji:

Minimalne czasy opóźnienia przed zapisem następnej komórki FLASH lub EEPROM

| Symbol | Opis | Minimalny czas opóźnienia |

| tWD_FLASH | Opóźnienie dla zapisu FLASH | 4,5 ms |

| tWD_EEPROM | Opóźnienie dla zapisu EEPROM | 4,0 ms |

| tWD_ERASE | Opóźnienie dla kasowania | 9,0 ms |

| tWD_FUSE | Opóźnienie dla zapisu bitu bezpiecznikowego | 4,5 ms |

| Instrukcja/operacja(1) | Format instrukcji | |||

| Bajt 1 | Bajt 2 | Bajt 3 | Bajt 4 | |

| Programming

Enable Włączenie programowania |

0xAC | 0x53 | 0x00 | 0x00 |

| Chip Erase Kasowanie (pamięć programu/EEPROM) |

0xAC | 0x80 | 0x00 | 0x00 |

| Poll RDY/BSY Podgląd stanu RDY/BSY |

0xF0 | 0x00 | 0x00 |

wyjściowy bajt danych |

| Instrukcje ładowania | ||||

| Load Extended

Address Byte Ładowanie bajtu rozszerzonego adresu |

0x4D | 0x00 |

rozszerzony adres |

0x00 |

| Load Program

Memory Page, High Byte Ładowanie strony pamięci programu, górny bajt |

0x48 |

MSB adresu |

LSB adresu |

wejściowy górny bajt danych |

| Load Program

Memory Page, Low Byte Ładowanie strony pamięci programu, dolny bajt |

0x40 |

MSB adresu |

LSB adresu |

wejściowy dolny bajt danych |

| Load EEPROM

Memory Page Ładowanie strony pamięci EEPROM (dostęp do strony) |

0xC1 | 0x00 |

LSB adresu |

wejściowy bajt danych |

| Instrukcje odczytu | ||||

| Read Program

Memory, High Byte Odczyt pamięci programu, górny bajt |

0x28 |

MSB adresu |

LSB adresu |

wyjściowy górny bajt danych |

| Read Program

Memory, Low Byte Odczyt pamięci programu, dolny bajt |

0x20 |

MSB adresu |

LSB adresu |

wyjściowy dolny bajt danych |

| Read EEPROM

Memory Odczyt pamięci EEPROM |

0xA0 | 0x00 |

LSB adresu |

wyjściowy bajt danych |

| Read Lock

Bits Odczyt bitów blokujących |

0x58 | 0x00 | 0x00 |

wyjściowy bajt danych |

| Read

Signature Byte Odczyt bajtu sygnatury |

0x30 | 0x00 |

LSB adresu |

wyjściowy bajt danych |

| Read Fuse

Bits Odczyt bitów bezpiecznikowych, dolny bajt |

0x50 | 0x00 | 0x00 |

wyjściowy bajt danych |

| Read Fuse

High Bits Odczyt bitów bezpiecznikowych, górny bajt |

0x58 | 0x08 | 0x00 |

wyjściowy bajt danych |

| Read Extended

Fuse Bits Odczyt bitów bezpiecznikowych, rozszerzony bajt |

0x50 | 0x08 | 0x00 |

wyjściowy bajt danych |

| Read

Calibration Byte Odczyt bajtu kalibracyjnego |

0x38 | 0x00 | 0x00 |

wyjściowy bajt danych |

| Instrukcje zapisu(2) | ||||

| Write Program

Memory Page Zapis strony pamięci programu |

0x4C |

MSB adresu |

LSB adresu |

0x00 |

| Write EEPROM

Memory Zapis pamięci EEPROM |

0xC0 | 0x00 |

LSB adresu |

wejściowy bajt danych |

| Write EEPROM

Memory Page Zapis strony pamięci EEPROM (dostęp do strony) |

0xC2 | 0x00 |

LSB adresu |

0x00 |

| Write Lock

Bits Zapis bitów blokujących |

0xAC | 0xE0 | 0x00 |

wejściowy bajt danych |

| Write Fuse

Bits Zapis dolnego bajtu bitów bezpiecznikowych |

0xAC | 0xA0 | 0x00 |

wejściowy bajt danych |

| Write Fuse

High Bits Zapis górnego bajtu bitów bezpiecznikowych |

0xAC | 0xA8 | 0x00 |

wejściowy bajt danych |

| Write

Extended Fuse Bits Zapis rozszerzonego bajtu bitów bezpiecznikowych |

0xAC | 0xA4 | 0x00 |

wejściowy bajt danych |

Przykład instrukcji

programowania szeregowego

Jeśli najmłodszy bit w wyjściowym bajcie danych RDY/BSY ma wartość "1", to operacja programowania nie została jeszcze zakończona. Odczekaj, aż bit ten przejdzie do stanu 0 przed wykonaniem następnej instrukcji.

Wewnątrz tej samej strony dolny bajt danych musi zostać załadowany przed górnym bajtem danych.

Po załadowaniu danych do bufora strony, zaprogramuj stronę EEPROM, zobacz na powyższy rysunek.

Znaczenie nazw końcówek w programowaniu wysokonapięciowym

| Nazwa sygnału | Końcówka | We/Wy | Funkcja |

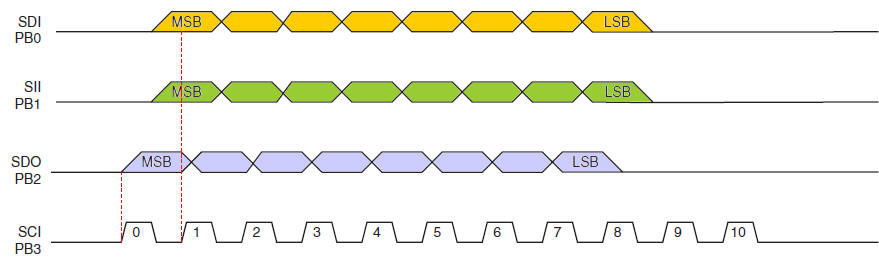

| SDI | PB0 | We | Szeregowe wejście danych (ang. Serial Data Input) |

| SII | PB1 | We | Szeregowe wejście instrukcji (ang. Serial Instruction Input) |

| SDO | PB2 | Wy | Szeregowe wyjście danych (ang. Serial Data Output) |

| SCI | PB3 | We | Szeregowe wejście zegara (ang. Serial Clock Input) |

Minimalny okres szeregowego wejścia zegarowego (SCI) podczas wysokonapięciowego programowania szeregowego wynosi 220 ns.

Wartości końcówek przy wejściu w tryb programowania

| Końcówka | Symbol | Wartość |

| PA0 | Prog_enable[0] | 0 |

| PA1 | Prog_enable[1] | 0 |

| PA2 | Prog_enable[2] | 0 |

Następujący algorytm wprowadza mikrokontroler w tryb wysokonapięciowego programowania szeregowego:

Jeśli czas narastania napięcia zasilającego VCC nie jest w stanie spełnić powyższych wymagań, można użyć alternatywnego algorytmu:

| Napięcie zasilania | Próg napięcia programowania na końcówce RESET |

Minimalny czas

zatrzaskiwania stanu końcówek Prog_enable |

| VCC | VHVRST | tHVRST |

| 4,5V | 11,5V | 100ns |

| 5,5V | 11,5V | 100ns |

Rozkaz Chip Erase skasuje zawartość pamięci FLASH i EEPROM (zawartość EEPROM zostaje zachowana podczas kasowania, jeśli został zaprogramowany bit bezpiecznikowy EESAVE) plus bity blokowania. Bity blokowania (ang. lock bits) nie są resetowane aż cała pamięć programu nie zostanie całkowicie skasowana. Bity bezpiecznikowe nie są zmieniane.

Rozkaz Chip Erase musi być wykonany przed przeprogramowaniem pamięci FLASH i/lub EEPROM.

Pamięć FLASH zorganizowana jest w strony. Gdy pamięć FLASH jest programowana, dane programu są zapamiętywane w buforze strony. Pozwala to zaprogramować jednocześnie całą stronę danych programu. Poniższa procedura opisuje programowanie całej pamięci FLASH:

Gdy zapisuje się lub odczytuje dane szeregowe z ATtiny25/45/85, dane są taktowane przy narastającym zboczu zegara szeregowego.

Adresowanie pamięci FLASH, która jest zorganizowana w strony

Przebiegi sygnałów w wysokonapięciowym programowaniu szeregowym

Pamięć EEPROM zorganizowana jest w strony. Gdy pamięć EEPROM jest programowana, dane są zapamiętywane w buforze strony. Pozwala to zaprogramować jednocześnie całą stronę danych. Algorytm programowania pamięci EEPROM jest następujący:

Algorytm odczytu pamięci FLASH jest następujący:

Algorytm odczytu pamięci EEPROM jest następujący:

Algorytmy programowania i odczytu bitów bezpiecznikowych i blokujących opisane są w tabeli instrukcji dla wysokonapięciowego programowania szeregowego.

Algorytmy są opisane w tabeli instrukcji dla wysokonapięciowego programowania szeregowego.

Ustaw SCI na "0". Ustaw RESET na "1". Wyłącz napięcie zasilania VCC.

| Instrukcja | Format Instrukcji | Uwagi na temat operacji | ||||

| Instr.1/5 | Instr.2/6 | Instr.3/7 | Instr.4 | |||

|

Chip Erase Kasowanie układu |

SDI SII SDO |

0_1000_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Po instrukcji 3 czekaj aż SDO wróci do stanu 1, aby cykl kasowania układu się zakończył. | |

| Load “Write

FLASH” Command Ładowanie rozkazu "Zapis FLASH" |

SDI SII SDO |

0_0001_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

Wprowadzenie kodu programowania FLASH. | |||

|

Load FLASH Page

Buffer Ładowanie bufora strony FLASH |

SDI SII SDO |

0_ bbbb_bbbb

_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_eeee_eeee_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1101_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Powtarzaj instr. 1 - 7, aż cały bufor strony zostanie wypełniony lub aż zostaną wypełnione wszystkie dany w obrębie strony.(2) |

| SDI SII SDO |

0_dddd_dddd_00 0_0011_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1101_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 x_xxxx_xxxx_xx |

Instr. 5 - 7. | ||

|

Load FLASH High

Address and Program Page Ładowanie górnego adresu FLASH i programowanie strony |

SDI SII SDO |

0_0000_000a_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Po instr. 3 czekaj, aż

SDO wróci do stanu wysokiego. Powtarzaj instr. 2 - 3

dla każdej załadowanej strony FLASH, aż cała pamięć

FLASH lub wszystkie dane zostaną zaprogramowane. Powtarzaj. instr. 1 dla nowej 256-bajtowej strony.(2) |

|

| Load “Read

FLASH” Command Ładowanie rozkazu "Odczyt FLASH" |

SDI SII SDO |

0_0000_0010_00 0_0100_1100_00 x_xxxx_xxxx_xx |

Wejście w tryb odczytu FLASH | |||

|

Read FLASH

Low and High Bytes Odczyt dolnego i górnego bajtu z FLASH |

SDI SII SDO |

0_bbbb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_0000_000a_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 q_qqqq_qqqx_xx |

Powtarzaj instrukcje 1, 3-6 dla każdego nowego adresu. Powtórz instr.2 dla nowej 256-bajtowej strony. |

| SDI SII SDO |

0_0000_0000_00 0_0111_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 p_pppp_pppx_xx |

Instr.5 - 6. | |||

| Load “Write

EEPROM” Command Załadowanie instrukcji "zapisu do EEPROM" |

SDI SII SDO |

0_0001_0001_00 0_0100_1100_00 x_xxxx_xxxx_xx |

Wejście w tryb programowania EEPROM. | |||

| Load

EEPROM Page Buffer Załadowanie bufora strony EEPROM |

SDI SII SDO |

0_bbbb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_aaaa_aaaa_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_eeee_eeee_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1101_00 x_xxxx_xxxx_xx |

Powtarzaj Instr.1-5, aż cały bufor będzie wypełniony lub gdy zostaną wypełnione wszystkie dane na stronie(3). |

| SDI SII SDO |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Instr. 5. | ||||

|

Program EEPROM Page Zaprogramowanie strony EEPROM |

SDI SII SDO |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Po Instr.2 czekaj aż SDO przejdzie w stan wysoki. Powtarzaj Instr.1-2 dla każdej załadowanej strony, aż zostanie zaprogramowana cała pamięć EEPROM lub wszystkie dane. | ||

| Write EEPROM Byte Zapis bajtu EEPROM |

SDI SII SDO |

0_bbbb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_aaaa_aaaa_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_eeee_eeee_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1101_00 x_xxxx_xxxx_xx |

Powtarzaj Instr.1-6 dla każdego nowego adresu. Po Instr.6 zaczekaj, aż SDO przejdzie w stan wysoki(4). |

| SDI SII SDO |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Instr. 5 - 6. | |||

| Load “Read

EEPROM” Command Załadowanie instrukcji "odczytu EEPROM" |

SDI SII SDO |

0_0000_0011_00 0_0100_1100_00 x_xxxx_xxxx_xx |

Wejście w tryb odczytu EEPROM. | |||

|

Read EEPROM Byte Odczyt bajtu z EEPROM |

SDI SII SDO |

0_bbbb_bbbb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_aaaa_aaaa_00 0_0001_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 q_qqqq_qqq0_00 |

Powtarzaj Instr.1,3-4

dla każdego nowego adresu. Powtórz Instr.2 dla nowej

256-bajtowej strony. |

| Write Fuse

Low Bits Zapis dolnych bitów bezpiecznikowych |

SDI SII SDO |

0_0100_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_A987_6543_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Po Instr.4 czekaj, aż SDO przejdzie w stan wysoki. Zapisz A-3 stanami "0", aby zaprogramować bity bezpiecznikowe. |

| Write Fuse

High Bits Zapis górnych bitów bezpiecznikowych |

SDI SII SDO |

0_0100_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_IHGF_EDCB_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 x_xxxx_xxxx_xx |

Po Instr.4 czekaj, aż SDO przejdzie w stan wysoki. Zapisz F-B stanami "0", aby zaprogramować bity bezpiecznikowe. |

|

Write Fuse

Extended Bits Zapis rozszerzonych bitów bezpiezcnikowych |

SDI SII SDO |

0_0100_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_000J_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0110_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1110_00 x_xxxx_xxxx_xx |

Po Instr.4 czekaj, aż SDO przejdzie w stan wysoki. Zapisz J stanem "0", aby zaprogramować bit bezpiecznikowy. |

| Write Lock

Bits Zapis bitów blokujących |

SDI SII SDO |

0_0010_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0021_00 0_0010_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_0100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_xxxx_xx |

Po Instr.4 czekaj, aż SDO przejdzie w stan wysoki. Zapisz 2-1 stanami "0", aby zaprogramować dany bit blokujący. |

| Read Fuse Low

Bits Odczyt dolnych bitów bezpiecznikowych |

SDI SII SDO |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 A_9876_543x_xx |

Odczyt A-3="0" oznacza bit bezpiecznikowy zaprogramowany. | |

| Read Fuse

High Bits Odczyt górnych bitów bezpiecznikowych |

SDI SII SDO |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1010_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 I_HGFE_DCBx_xx |

Odczyt I-B="0" oznacza bit bezpiecznikowy zaprogramowany. | |

|

Read Fuse Extended

Bits Odczyt rozszerzonych bitów bezpiecznikowych |

SDI SII SDO |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1010_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1110_00 x_xxxx_xxJx_xx |

Odczyt J="0" oznacza bit bezpiecznikowy zaprogramowany. | |

| Read Lock

Bits Odczyt bitów blokujących |

SDI SII SDO |

0_0000_0100_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 x_xxxx_x21x_xx |

Odczyt 2, 1 ="0" oznacza bit blokujący zaprogramowany. | |

| Read

Signature Bytes Odczyt bajtów sygnaturowych |

SDI SII SDO |

0_0000_1000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_00bb_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0110_1100_00 q_qqqq_qqqx_xx |

Powtórz Instr.2-4 dla każdego adresu bajtu sygnatury. |

| Read

Calibration Byte Odczyt bajtu kalibracyjnego |

SDI SII SDO |

0_0000_1000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0000_1100_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1000_00 x_xxxx_xxxx_xx |

0_0000_0000_00 0_0111_1100_00 p_pppp_pppx_xx |

|

| Load “No

Operation” Command Załadowanie instrukcji pustej |

SDI SII SDO |

0_0000_0000_00 0_0100_1100_00 x_xxxx_xxxx_xx |

||||

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.