Autor artykułu: mgr Jerzy Wałaszek, wersja1.0

Konsultacja: Wojciech Grodowski

©2013 mgr

Jerzy Wałaszek

I LO w Tarnowie

|

Autor artykułu: mgr Jerzy Wałaszek, wersja1.0 Konsultacja: Wojciech Grodowski |

©2013 mgr

Jerzy Wałaszek

|

Współczesne komputery zbudowane są z milionów elementów logicznych zwanych bramkami cyfrowymi lub bramkami logicznymi (ang. digital gate). Są to elementy elektroniczne posiadające wejścia oraz wyjście danych:

|

Na wejścia bramki podajemy napięcia elektryczne, które mogą przyjmować dwa poziomy logiczne (dla układów TTL - Transistor-Transistor-Logic):

| poziom 0, L, F | - napięcie w przedziale 0...0,8V |

| poziom 1, H, T | - napięcie w przedziale 2...5V |

Poziomy te odpowiadają ściśle wartościom logicznym stosowanym w Algebrze Boole'a. Poziom logiczny 0 jest oznaczany często literką L od Low, czyli niski lub literką F od False, czyli fałsz. Podobnie poziom logiczny 1 jest oznaczany literką H od High, czyli wysoki lub literką T od True, czyli prawda. Wynika z tego, iż w technice cyfrowej bity są reprezentowane poziomami napięć elektrycznych (ta uwaga jest dla tych, którzy myślą, iż w komputerze jest dużo zer i jedynek - dosłownie... :) ).

Na wyjściu bramki również dostajemy napięcie elektryczne mieszczące się w przedziale dla 0 lub 1. Napięcie to jest funkcją logiczną (np. negacją, alternatywą, koniunkcją itp.) realizowaną przez bramkę dla napięć wejściowych. W produkcji są bramki realizujące wszystkie podstawowe funkcje logiczne Algebry Boole'a. Nie będziemy się zajmować budową wewnętrzną bramki logicznej. Składa się ona z odpowiednio połączonych ze sobą elementów elektronicznych zwanych tranzystorami i opornikami. Zrozumienie ich funkcji wymaga dosyć zaawansowanych wiadomości z zakresu elektroniki elementów półprzewodnikowych, zatem darujemy sobie ten dział wiedzy, gdyż w sumie nie będzie nam on potrzebny. Potraktujemy bramkę logiczną jak czarną skrzynkę, na której wejścia podaje się odpowiednie napięcia elektryczne, a na wyjściu otrzymuje się napięcie wynikowe w funkcji napięć wejściowych - takie podejście jest zupełnie wystarczające do projektowania nawet bardzo złożonych sieci cyfrowych. Jednakże bez kilku parametrów się nie obejdzie.

Wyjścia bramek można łączyć z wejściami innych bramek logicznych (samych wyjść nie wolno ze sobą łączyć, ponieważ prowadzi to do zwarcia i w konsekwencji do uszkodzenia bramki) - w ten sposób powstaje sieć logiczna realizująca złożoną funkcję logiczną. Każde wejście bramki dołączone do wyjścia innej bramki pobiera z niej pewien prąd elektryczny. Wyjścia bramek mogą dostarczyć tylko określoną ilość prądu. Wynika z tego, iż do typowego wyjścia można podłączyć ograniczoną ilość wejść innych bramek. Parametr ten nosi nazwę obciążalności wyjścia bramki. Zwykle przyjmuje się go na poziomie 10 (należy sprawdzić w danych producenta) dla zwykłych bramek oraz 30 dla bramek o zwiększonej mocy wyjściowej.

Obciążalności wyjściowej bramki nie należy przekraczać, gdyż może to spowodować niestabilność sieci logicznej (kłopoty z utrzymaniem odpowiedniego poziomu napięcia wyjściowego przez przeciążoną bramkę), a nawet spalenie niektórych jej elementów.

Zapamiętaj:Obciążalność wyjścia bramki logicznej określa ile wejść innych bramek można podłączyć do tego wyjścia. Dla typowych bramek obciążalność wyjścia wynosi 10. |

Poziom napięcia wyjściowego bramki jest funkcją logiczną Boole'a poziomu logicznego napięć wejściowych. Napięcie na wyjściu nie zmienia się natychmiast po zmianie poziomu napięć wejściowych, lecz po pewnym czasie - typowo po 10 ns (należy sprawdzić w danych producenta). Jest to spowodowane tym, iż tranzystory wewnątrz bramki muszą się odpowiednio przełączyć, a to wymaga nieco czasu.

Zapamiętaj:Czas propagacji bramki logicznej określa po jakim czasie od zmiany napięć wejściowych ustali się napięcie na wyjściu. Czas propagacji typowo wynosi 10 ns dla bramek standardowych i 3 ns dla bramek serii szybciej. Im mniejszy czas propagacji, tym szybciej może pracować bramka. |

Czas propagacji dla sieci logicznej jest sumą czasów propagacji bramek, poprzez które przechodzi kolejno sygnał logiczny. Czasy te zawsze należy brać pod uwagę przy projektowaniu układów logicznych. W przeciwnym razie może wystąpić tzw. zjawisko hazardu.

Na schematach elektronicznych (rysunkach obrazujących sposób połączenia wejść i wyjść bramek logicznych tworzących sieć logiczną) bramki cyfrowe są reprezentowane przez unormowane symbole graficzne. Poniżej przedstawiamy te symbole wraz z opisem funkcji logicznej realizowanej przez daną bramkę. Pamiętaj, iż symbole 0 i 1 oznaczają w rzeczywistości odpowiednie poziomy napięć logicznych.

W symulacjach bramek i sieci logicznych kolor czerwony oznacza stan wysoki 1, kolor niebieski oznacza stan niski 0.

Bramka NOT realizuje operację negacji logicznej: y = a. W technice cyfrowej negację zaznaczamy albo jako NOT a, albo a.

| Bramka NOT

|

|

Bramka NOT często nazywana jest negatorem lub inwerterem, ponieważ "odwraca" poziom napięcia logicznego z wejścia. Symbol kółeczka na wyjściu lub wejściu oznacza negację sygnału.

Bramka AND realizuje operację koniunkcji logicznej y = ab. W technice cyfrowej koniunkcję oznaczamy jako a AND b lub ab.

| Bramka AND

|

|

Bramki logiczne mogą posiadać więcej niż dwa wejścia. Na przykład poniżej przedstawiamy bramkę AND trójwejściową. Bramka realizuje funkcję logiczną y = abc.

| Trójwejściowa bramka AND

|

|

Bramka OR realizuje operację alternatywy logicznej y = a+b. W technice cyfrowej alternatywę oznaczamy jako a OR b lub a+b.

| Bramka OR

|

|

Zgodnie z prawami De Morgana każdą funkcję logiczną da się sprowadzić do kombinacji negacja/koniunkcja lub negacja/alternatywa. Dlatego przemysł elektroniczny produkuje tzw. bramki uniwersalne NAND = NOT/AND i NOR = NOT/OR, z których da się budować dowolne sieci logiczne. Korzyść jest oczywista – w budowanym urządzeniu stosujemy jeden typ elementów, co obniża koszty produkcji. Na schematach logicznych bramki NAND i NOR mogą posiadać dwa różne symbole (oparte na prawach De Morgana).

| Bramka NAND

|

|

Bramka NOR

|

|

Poniżej przedstawiamy sposoby uzyskania podstawowych funkcji logicznych przy pomocy bramek uniwersalnych NAND i NOR.

| Bramka NOT

|

= | z bramki NAND

|

= | z bramki NOR

|

| Bramka OR

|

= | z bramek NAND

|

= | z bramek NOR

|

| Bramka AND

|

= | z bramek NAND

|

= | z bramek NOR

|

Musimy jednakże pamiętać, iż takie rozwiązanie jest gorsze od zastosowania właściwej bramki logicznej – zwiększa się obciążenie wyjść bramek sterujących (w niektórych układach łączone ze sobą dwa wejścia bramki) oraz zwiększa się czas propagacji (bramki pracują szeregowo)

W latach 60 ubiegłego wieku wynaleziono układy scalone. Są to małe elementy elektroniczne zawierające w swojej strukturze gotowe układy zbudowane z dziesiątek, setek, tysięcy lub więcej tranzystorów. Dzięki układom scalonym stała się możliwa budowa współczesnych komputerów. Nawet najprostszy komputer IBM składa się wewnętrznie z milionów tranzystorów. Bez układów scalonych budowa takiego komputera byłaby bardzo kosztowna i czasochłonna – na pewno nie byłoby nas stać na własny, domowy komputer osobisty.

Bramki cyfrowe są umieszczane w układach scalonych, które produkuje wiele różnych firm na całym świecie. Najpopularniejsze serie to TTL (bramki zbudowane z tzw. tranzystorów bipolarnych) oraz CMOS (bramki zbudowane z tranzystorów polowych).

| Parametr | TTL | CMOS |

| Zasilanie | 5V | 3...15V |

| Poziom 0 | 0,4...0,8V | 0V |

| Poziom 1 | 2...5V | VDD |

| Czas propagacji | 1,5...3 ns | 30 ns |

| Obciążalność wyjść | 10 | duża |

Układy TTL są zwykle 10 razy szybsze od układów CMOS (chociaż niektóre współczesne konstrukcje CMOS niewiele ustępują w szybkości układom TTL). Za to układy CMOS mogą być zasilane napięciem o dużej rozpiętości oraz pobierają znikomą moc (szczególnie istotne dla urządzeń zasilanych bateryjnie).

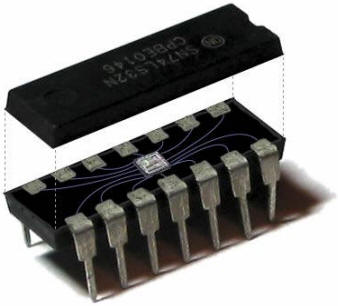

Z zewnątrz układ scalony przypomina małą kostkę z wyprowadzonymi metalowymi końcówkami, do których doprowadzamy lub z których pobieramy sygnały elektryczne. Wewnątrz układu scalonego wyprowadzenia są połączone z małą płytką silikonową, na której w drodze skomplikowanych procesów utworzono strukturę elektroniczną złożoną z setek lub tysięcy tranzystorów i oporników.

Nóżki układu scalonego są odpowiednio numerowane. Zwróć uwagę, iż na obudowie znajduje się małe wycięcie lub mała dziurka. Układ ustawiamy nóżkami w dół, tak aby wcięcie na obudowie znalazło się po stronie lewej. Wtedy numeracja nóżek rozpoczyna się od lewego dolnego rogu i biegnie wokół układu scalonego. Poniżej przedstawiamy widok z góry układu o 14 wyprowadzeniach.

Gdy umiemy już odczytywać numery wyprowadzeń układów scalonych, możemy zdefiniować ich zawartość. Poniżej przedstawiamy definicje wyprowadzeń kilku układów cyfrowych zawierających podstawowe bramki logiczne. Są to układy TTL serii SN74xx oraz CMOS serii CD40xx. GND oznacza masę dla TTL (minus zasilania), VSS dla CMOS. VCC oznacza napięcie zasilające układ scalony TTL (+5V), VDD dla CMOS. Wiedza ta pozwala na samodzielne konstruowanie prostych urządzeń cyfrowych. Układy zestawiliśmy, tak aby w obu seriach otrzymać funkcjonalne odpowiedniki. Dlatego kolejność numeracji układów CMOS nie jest zachowana.

| Układy TTL serii SN74xx | Układy CMOS serii CD40xx |

| SN7400 – cztery

2-wejściowe bramki uniwersalne NAND

|

CD4011 – cztery

2-wejściowe bramki uniwersalne NAND

|

| SN7402 – cztery

2-wejściowe bramki uniwersalne NOR

|

CD4001 – cztery

2-wejściowe bramki uniwersalne NOR

|

| SN7404 – sześć

inwerterów

|

CD4009 – sześć

inwerterów

|

| SN7407 – sześć

wzmacniaczy buforowych

|

CD4010

– sześć wzmacniaczy buforowych

|

| SN7408 – cztery

2-wejściowe bramki AND

|

CD4081 – cztery

2-wejściowe bramki AND

|

| SN7410 – trzy

3-wejściowe bramki uniwersalne NAND

|

CD4023 – trzy

3-wejściowe bramki uniwersalne NAND

|

| SN7411 – trzy

3-wejściowe bramki AND

|

CD4073 – trzy

3-wejściowe bramki AND

|

| SN7420 – dwie

4-wejściowe bramki uniwersalne NAND

|

CD4012 – dwie

4-wejściowe bramki uniwersalne NAND

|

| SN7421 – dwie

4-wejściowe bramki AND

|

CD4082 – dwie

4-wejściowe bramki AND

|

| SN7427 – trzy

3-wejściowe bramki uniwersalne NOR

|

CD4025 – trzy

3-wejściowe bramki uniwersalne NOR

|

| SN7430 – jedna

8-wejściowa bramka uniwersalna NAND

|

CD4068 – jedna

8-wejściowa bramka uniwersalna NAND

|

| SN7432 – cztery

2-wejściowe bramki OR

|

CD4071 – cztery

2-wejściowe bramki OR

|

Do jednego wyjścia bramki można podłączyć kilka wejść innych bramek. Musimy tylko pamiętać, aby nie przekroczyć obciążalności wyjścia bramki. Typowe wyjście bramki TTL może wysterować około 10 wejść innych bramek. Do bramek CMOS reguła ta się nie odnosi, ponieważ pobierają one bardzo mały prąd wejściowy – mówimy, iż posiadają dużą oporność wejściową.

Nieużywane wejścia bramek należy podłączyć poprzez opornik 1kΩ (jeśli możemy zagwarantować, iż napięcie VCC nie przekroczy 5,5V, to wejście można połączyć bezpośrednio) do zasilania +5V (bramki AND i NAND) lub bezpośrednio do masy (bramki OR i NOR). Nie wolno pozostawiać wejścia "wiszącego", ponieważ powoduje to pogorszenie warunków pracy bramki (zwiększa się czas propagacji oraz zmniejsza się odporność na zakłócenia) i w konsekwencji może powodować błędy w działaniu urządzenia cyfrowego.

Nie wolno łączyć ze sobą wyjść bramek, gdyż prowadzi to do zwarcia i w konsekwencji może uszkodzić układ cyfrowy.

Z diodami

LED spotkaliśmy się na poprzednich zajęciach. Powtórzmy sobie podstawowe

wiadomości.

Z diodami

LED spotkaliśmy się na poprzednich zajęciach. Powtórzmy sobie podstawowe

wiadomości.

Dioda LED (ang. Light Emitting Diode) jest elementem elektronicznym, który przewodzi prąd tylko w jednym kierunku. Gdy prąd płynie przez diodę LED, emituje ona światło. Kolor świecenia zależy od materiału użytego do konstrukcji diody.

Diody LED bardzo często wykorzystywane są w technice cyfrowej jako różnego rodzaju wskaźniki i oświetlenie – np. zegary wyświetlają przy ich pomocy cyfry czasu i daty, telefony komórkowe używają ich do podświetlania swoich ekranów i klawiatur. Stosując diody LED, należy pamiętać o rzeczach następujących:

|

Zwykle diody o średnicy 5mm (najbardziej popularne cenowo) pobierają prąd IF = 20mA. Jeśli chcemy uzyskać niezawodność świecenia, to obniżamy ten prąd do 15mA (tyle może na wyjściu dostarczyć standardowa bramka TTL). Napięcie UF określamy z poniższej tabelki:

| Rodzaj diody LED | Napięcie UF | Prąd IF |

| zwykłe, czerwone | 1,7V | 15mA |

| jasne, czerwone wysokowydajne, czerwone niskoprądowe, czerwone |

1,9V | 15mA |

| pomarańczowe i żółte | 2V | 15mA |

| zielone | 2,1V | 15mA |

| jasne, białe jasne, zielone bez żółtozielonego niebieskie zwykłe |

3,4V | 12mA |

| jasne, niebieskie | 4,6V | 10mA |

Do naszych celów najlepsze będą diody o UF = 1,7V ... 2,1V. Diody o wyższym napięciu wymagają tranzystora sterującego, który zapewni im odpowiednie warunki zasilania. Diodę LED można podłączyć do wyjścia bramki TTL na dwa sposoby. W obu przypadkach należy odpowiednio dobrać opór ograniczający napięcie i prąd diody LED. Poniżej przedstawiamy odpowiednie wzory obliczeniowe:

| Dioda świeci przy stanie wysokim

|

Dioda świeci przy stanie niskim

|

|

|

| Dla diody czerwonej o UF = 1,7V i IF = 0,015A otrzymamy: | |

|

|

Dla wersji pierwszej napięcie 3,5V jest napięciem wyjściowym bramki TTL w stanie wysokim. Napięcie to rozkłada się na opornik R oraz diodę LED. Gdy odejmiemy od niego napięcie UF diody LED, to pozostanie napięcie na oporniku R. Dzieląc to napięcie przez pożądany prąd IF otrzymujemy wartość opornika R, którą należy w tym układzie zastosować.

Dla wersji drugiej jest podobnie. Napięcie 4,6V jest napięciem zasilania pomniejszonym o napięcie 0,4V, które pojawia się na wyjściu bramki w stanie niskim.

Powyższe dwa układy można połączyć w jeden – górna dioda LED będzie świeciła w stanie niskim, a dolna dioda LED będzie świeciła w stanie wysokim.

Dobierając oporniki pamiętaj, iż w sprzedaży są wartości tworzące następujące szeregi:

| E3 | 50% | 10, 22, 47 |

| E6 | 20% | 10, 15, 22, 33, 47, 68 |

| E12 | 10% | 10, 12, 15, 18, 22, 27, 33, 39, 47, 56, 68, 82 |

| E24 | 5% | 10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62, 68, 75, 82, 91 |

Wartości w szeregach mogą być mnożone przez potęgi liczby 10. W ten sposób otrzymujemy np. 33 x 1000 = 33kΩ. To dlatego w drugim przykładzie zaokrągliłem wynik 193,333... do najbliższej, dostępnej wartości 200W (szereg E24, wartość 20 x 10). To małe oszustwo nie wpłynie w sposób istotny na działanie opisywanego układu.

Więcej na temat szeregów oporników i kondensatorów znajdziesz w dowolnym podręczniku elektroniki oraz w Wikipedii.

Zaprojektujemy teraz prosty układ z dwóch bramek NAND (bramki pracują jako inwertery, możemy też zastosować bramki NOT). Schemat jest następujący:

Za pomocą podanych wyżej wzorów obliczamy wartości oporów R1 i R2.

Przyjmujemy R1 = 180Ω

Przyjmujemy R2 = 100Ω.

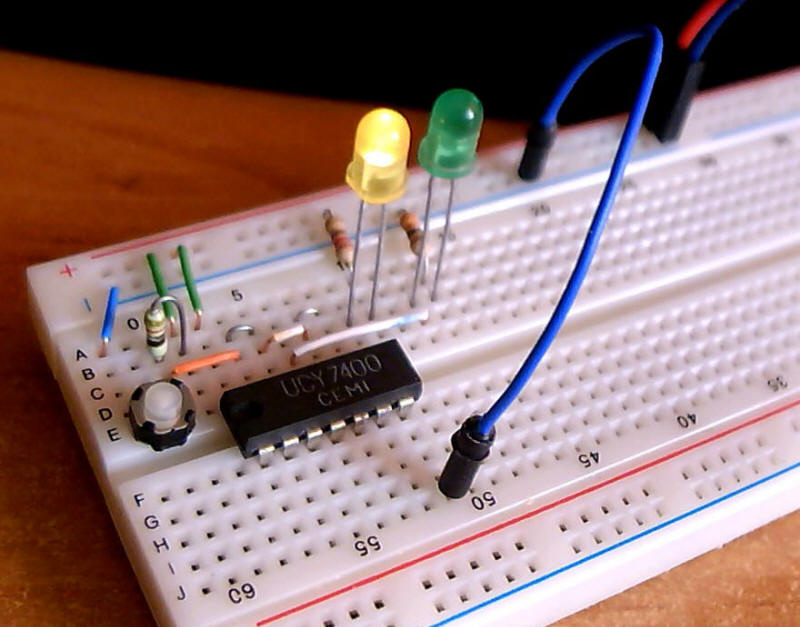

Podsumujmy spis elementów:

| Element | Ilość | Opis |

| zasilacz 5V | 1 | do zasilania elementów elektronicznych |

| płytka stykowa + kable | 1 | do montażu elementów elektronicznych |

| SN7400 | 1 | 4 bramki NAND (lub SN7404) |

| opornik 1kΩ/0,125W | 1 | –( )– do podłączania wejść bramek do +5V |

| opornik 180Ω/0,125W | 1 | –( )– do ograniczania napięcia i prądu żółtej diody LED |

| opornik 100Ω/0,125W | 1 | –( )– do ograniczania napięcia i prądu zielonej diody LED |

| zielona dioda LED | 1 | do sygnalizacji stanu wysokiego na wyjściu bramki NAND |

| żółta dioda LED | 1 | do sygnalizacji stanu niskiego na wyjściu bramki NAND |

| mikroprzełącznik | 1 | do zmiany stanu logicznego na wejściach bramek |

Koszt elementów nie powinien przekroczyć 3zł. Układ zmontuj na płytce stykowej wg podanego powyżej schematu.

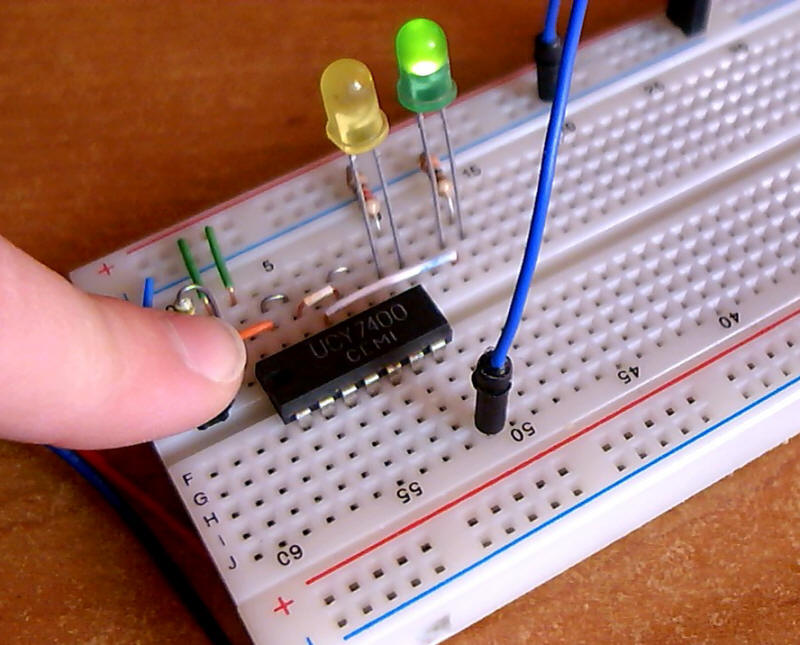

Widoczny na zdjęciu układ UCY7400 jest odpowiednikiem SN7400, który był kiedyś produkowany w Polsce i pochodzi ze "starych" zapasów.

Niebieskim przewodem jest podłączona masa układu do minusa zasilania.

Po zmontowaniu i podłączeniu zasilania zapala się dioda żółta. Dzieje się tak dlatego, że wejścia bramek są podłączone poprzez opornik 1kΩ do +5V, co wymusza na nich stan wysoki. Jeśli na obu wejściach bramki NAND jest stan wysoki, to na jej wyjściu pojawi się stan niski 0,4V. Napięcie takie jest zbyt małe, aby zapalić diodę zieloną w dolnej bramce. Jednakże w górnej bramce na oporniku i diodzie żółtej odkłada się napięcie 5V pomniejszone o napięcie wyjściowe 0,4V górnej bramki. Napięcie to jest wystarczająco duże, aby świeciła dioda żółta.

Jeśli teraz naciśniesz przycisk, to zewrzesz wejścia bramek NAND do masy, co jest równoważne z podaniem na ich wejścia stanu niskiego. Przy stanie niskim na wejściach na wyjściu bramki NAND pojawia się stan wysoki 2,5...3,5V. Napięcie to jest wystarczające, aby zapalić diodę zieloną. Na diodzie żółtej i jej oporniku teraz panuje napięcie 5V - 3,5V = 1,5V. A to jest zbyt mało, aby dioda żółta mogła się świecić. Dlatego dioda żółta gaśnie, a zapala się dioda zielona. Gdy zwolnisz przycisk, układ powróci do stanu początkowego i znów zapali się dioda żółta, a zielona zgaśnie.

Gratulacje!

Zmontowałeś pierwszy układ cyfrowy.

| I Liceum Ogólnokształcące |

Pytania proszę przesyłać na adres email: i-lo@eduinf.waw.pl

W artykułach serwisu są używane cookies. Jeśli nie chcesz ich otrzymywać,

zablokuj je w swojej przeglądarce.

Informacje dodatkowe