Autor artykułu: mgr Jerzy Wałaszek, wersja1.0

Konsultacja: Wojciech Grodowski

©2013 mgr

Jerzy Wałaszek

I LO w Tarnowie

|

Autor artykułu: mgr Jerzy Wałaszek, wersja1.0 Konsultacja: Wojciech Grodowski |

©2013 mgr

Jerzy Wałaszek

|

Przerzutnik (ang. flip flop) jest układem cyfrowym wyposażonym w pamięć. W przypadku bramki cyfrowej stan jej wyjścia jest bezpośrednio uzależniony od stanów panujących na wejściach - opisuje to funkcja logiczna realizowana przez bramkę. W przerzutniku jest nieco inaczej - zapamiętuje on swój stan wewnętrzny. Stan ten może być zmieniony przez odpowiednie wysterowanie wejść.

Pierwszy elektroniczny przerzutnik typu flip-flop wynaleziony został w roku 1919 przez dwóch naukowców - Williama Ecclesa i F.W. Jordana. Początkowo nazywano go układem przełączającym Ecclesa-Jordana. Układ ten zbudowany był z dwóch aktywnych elementów elektronicznych - lamp elektronowych (pierwsze tranzystory powstały dopiero w 1949 roku). Angielska nazwa flip flop powstała później jako efekt naśladowania dźwięku wydawanego przez głośniki podłączone do wzmacniacza akustycznego sterowanego przez wymieniony przerzutnik.

Przerzutnik RS (od ang. RS flip flop lub SR flip flop - Set Reset - Ustaw, Zeruj) jest najprostszym rodzajem przerzutnika, który można zbudować z dwóch dwu wejściowych bramek NOR lub NAND. Przerzutnik powstaje dzięki sprzężeniu zwrotnemu (ang. feed back) wyjść z wejściami. Sprzężenie zwrotne powoduje, iż przerzutnik utrzymuje ostatni stan wyjść Qn-1 po przejściu stanów logicznych na wejściach w stan neutralny. Poniżej przedstawiamy symulację przerzutnika RS z bramek NAND i NOR. Kreseczka ponad opisem wejścia lub wyjścia oznacza tutaj negację.

| Przerzutnik SR z bramek NAND | Przerzutnik RS z bramek NOR | |||||||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||

W przerzutniku SR zbudowanym z bramek NAND wejścia S i R są aktywne przy stanie 0. Stan 1 jest dla nich stanem neutralnym. Jeśli wejście S przejdzie w stan 0, to wymusi ono stan 1 na wyjściu Q. Przejście wejścia R w stan 0 wymusi stan 0 na wyjściu Q. Powrót wejść S i R do stanu neutralnego nie zmienia stanu logicznego wyjścia Q - przerzutnik zapamiętuje ustawiony stan logiczny. Jeśli oba wejścia S i R znajdą się w stanie niskim 0, będziemy mieli do czynienia ze stanem zabronionym - oba wyjścia Q i Q znajdą się w stanie wysokim 1. Powrót jednego z wejść S lub R do stanu neutralnego 1 wymusi odpowiedni stan przerzutnika. Problem jednakże pojawi się, jeśli oba wejścia S i R jednocześnie przejdą ze stanu 0 do stanu 1. W takim przypadku stan przerzutnika będzie zależał od wewnętrznych hazardów i wynik jest nieokreślony, tzn. na wyjściu Q może pojawić się zarówno stan 0 jak i stan 1 - nie da się przewidzieć, który z tych stanów ustali się w przerzutniku.

W przerzutniku RS zbudowanym z bramek NOR wejścia R i S są aktywne przy stanie logicznym 1. Stanem neutralnym jest dla nich stan 0. Jeśli wejście S przejdzie w stan 1, to wymusi ono stan 1 na wyjściu Q. Podobnie stan 1 na wejściu R wymusza stan 0 na wyjściu Q. Stanem zabronionym jest stan 1 na obu wejściach R i S przerzutnika. W takim przypadku oba wyjścia Q i Q przechodzą w stan 0. Jeśli teraz wejścia S i R przejdą jednocześnie w stan neutralny 0, to wynikowy stan wyjścia Q jest nieokreślony - może być równy 1 lub 0 w zależności od wewnętrznych hazardów w sieci logicznej przerzutnika, nie daje się przewidzieć.

Przerzutniki RS często są stosowane do odczytu stanu przełączników mechanicznych. Przełączniki te mają taką własność, iż w momencie przełączenia styki często wykonują drgania sprężyste, co powoduje powstawanie serii krótkich impulsów napięciowych, które mogą być szkodliwe dla układów cyfrowych:

Rozwiązaniem jest zastosowanie przerzutnika SR z bramek NAND.

Drgania styków nie przeniosą się na wyjście, ponieważ sygnał wejściowy S lub R ustawi odpowiednio stan Y i ewentualne zmiany tego sygnału nie spowodują już zmiany poziomu logicznego wyjścia Y.

|

SN7400 |

Działanie jest następujące:

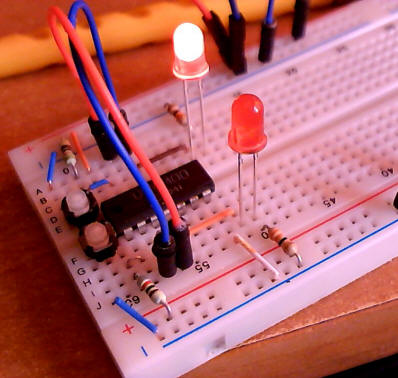

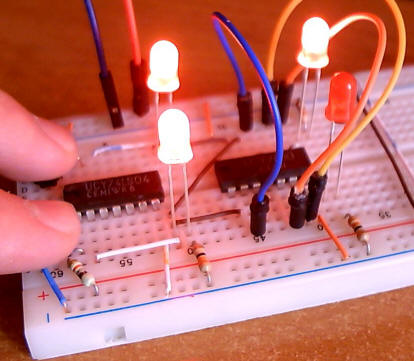

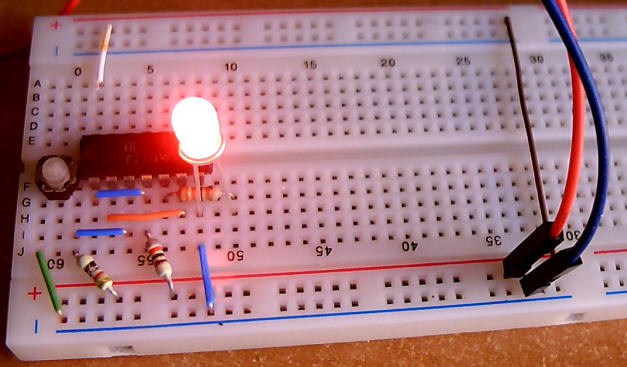

Spis elementów:

| Element | Ilość | Opis |

| zasilacz 5V | 1 | do zasilania elementów elektronicznych |

| płytka stykowa + kable | 1 | do montażu elementów elektronicznych |

| SN7400 | 1 | 4 bramki NAND |

| opornik 1kΩ/0,125W | 2 | –( )– do podłączania wejść bramek do +5V |

| opornik 120Ω/0,125W | 2 | –( )– do ograniczania napięcia i prądu diod LED |

| czerwona dioda LED | 2 | do sygnalizacji stanu wysokiego na wyjściu bramki NAND |

| mikroprzełącznik | 2 | do zmiany stanu logicznego na wejściach bramek |

W przerzutniku D latch stan wejścia D jest kopiowany na wyjście Q przy wysokim poziomie logicznym na wejściu C. Gdy poziom wejścia C zmieni się na niski, przerzutnik zapamiętuje ostatni stan wyjścia Q. Zmiany na wejściu informacyjnym D nie wpływają już na wyjście Q, które zostało "zatrzaśnięte" zmianą poziomu wejścia C - z tego powodu przerzutniki te noszą często nazwę zatrzask. Poniżej przedstawiamy symulację sieci logicznej przerzutnika D typu Latch.

|

|

Wejście C nosi nazwę wejścia zegarowego (ang. Clock input). Umożliwia ono synchronizację działania poszczególnych elementów sieci logicznej. Np. przerzutniki typu D Latch są często stosowane jako rejestry (układy pamiętające ciąg bitów). W takim przypadku zapis danych do wszystkich rejestrów jest wykonywany za pomocą pojedynczego impulsu na wejściach C, które są ze sobą połączone:

4-bitowy rejestr z przerzutników D Latch

Sieć logiczna przerzutnika D Latch działa następująco:

Gdy na wejściu C panuje stan logiczny 0. to na wyjściu górnej bramki wejściowej jest stan logiczny 1 bez względu na stan wejścia D (sprawdź to z tabelką stanów logicznych bramki NAND). Powoduje to, że na wyjściu dolnej bramki wejściowej również panuje stan 1. Wejścia przerzutnika RS są zatem w stanie wysokim 1. Przy takim wysterowaniu wejść przerzutnik RS pamięta swój poprzedni stan.

Gdy stan wejścia C zmienia się na 1, to wyjście górnej bramki przyjmuje stan zależny od wejścia D: 1, gdy D = 0, lub 0, gdy D = 1. Zwróć uwagę, że wtedy wyjście dolnej bramki wejściowej zawsze przyjmuje stan przeciwny od stanu wyjścia bramki górnej. Zatem, jeśli na górnej bramce jest stan 1, to na dolnej mamy stan 0 i na odwrót. Stany te powodują ustawienie przerzutnika RS: gdy D = 0, to przerzutnik zostaje wyzerowany, gdy D = 1, to przerzutnik zostaje ustawiony na 1.

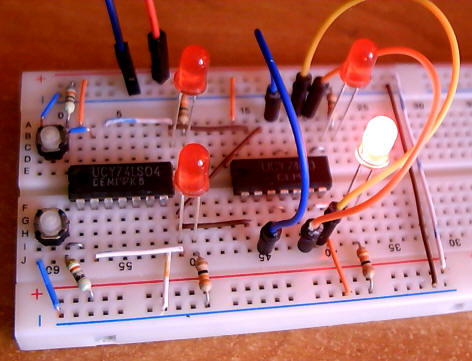

W układzie ćwiczeniowym dodamy dwa inwertery, aby wygodnie sterować wejściami przerzutnika (naciśnięcie przycisku będzie powodowało, że na wejściu przerzutnika D pojawi się stan 1). Schemat układu jest następujący:

|

SN7404 |

SN7400 |

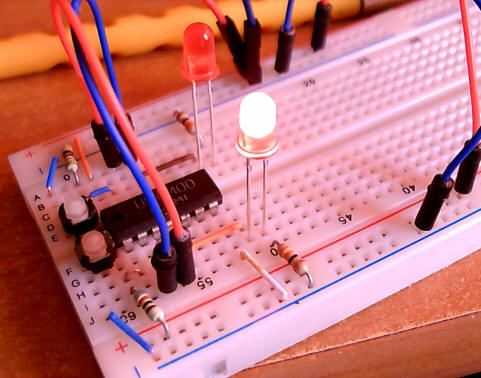

Spis elementów:

| Element | Ilość | Opis |

| zasilacz 5V | 1 | do zasilania elementów elektronicznych |

| płytka stykowa + kable | 1 | do montażu elementów elektronicznych |

| SN7400 | 1 | 4 bramki NAND |

| SN7404 | 1 | 6 inwerterów NOT |

| opornik 1kΩ/0,125W | 2 | –( )– do podłączania wejść bramek do +5V |

| opornik 120Ω/0,125W | 4 | –( )– do ograniczania napięcia i prądu diod LED |

| czerwona dioda LED | 4 | do sygnalizacji stanu wysokiego na wyjściach/wejściach układu |

| mikroprzełącznik | 2 | do zmiany stanu logicznego wejść D i C |

W momencie naciśnięcia dolnego przycisku (C) stan górnego przycisku (D) jest przepisywany na wyjście Q przerzutnika. Jeśli górny przycisk nie jest naciśniety, to dioda na wyjściu Q będzie zgaszona, ponieważ wejście D jest w stanie niskim. Jeśli górny przycisk jest wciśnięty, to na wejściu D pojawia się stan wysoki i przenosi się on na wyjście Q. Gdy dolny przycisk zostanie zwolniony, przerzutnik utrzymuje ostatnio wpisany do niego stan – pamięta wprowadzoną informację. Teraz naciskanie górnego przycisku nie powoduje żadnych zmian przerzutnika.

Otrzymaliśmy prosty model komórki pamięci komputera. Wejście zegarowe C możemy potraktować jako wejście wpisujące informację do komórki, czyli do naszego przerzutnika D.

W praktyce nie tworzy się zwykle przerzutników D z pojedynczych bramek. Przemysł elektroniczny produkuje odpowiednie układy scalone, które zawierają gotowe przerzutniki D Latch. Stosujemy je tam, gdzie występuje potrzeba zapamiętania jakiś stanów logicznych.

SN7475 4 przerzutniki D Latch

Przerzutnik D Latch zapamiętywał stan wejścia D, gdy sygnał zegarowy C przechodził ze stanu 1 na 0. Podczas trwania sygnału C na poziomie logicznym 1 zmiany wejścia D automatycznie przenoszą się na wyjście Q. O takim przerzutniku mówimy, że jest wyzwalany poziomem sygnału zegarowego (ang. level triggered flip flop).

Możemy jednak skonstruować przerzutnik D, tak aby zapamiętywał on stan wejścia D w momencie przejścia sygnału zegarowego ze stanu 1 na 0, lecz w trakcie trwania stanu C = 1 zmiany na wejściu D nie przenoszą się na wyjście Q. Przerzutnik wciąż pamięta swój poprzedni stan. Zmiana na wyjściu Q pojawi się dopiero przy zmianie C z 1 na 0. O takim przerzutniku mówimy, że jest wyzwalany zboczem sygnału (ang. edge triggered flip flop). Na schematach zaznacza się to w odpowiedni sposób:

|

|

wyzwalanie poziomem 1 |

|

|

wyzwalanie poziomem 0 |

|

|

wyzwalanie zboczem dodatnim: 0 → 1 |

|

|

wyzwalanie zboczem ujemnym: 1 → 0 |

Przerzutnik D wyzwalany zboczem ujemnym zawiera dwa przerzutniki D Latch, które pracują w tzw. trybie Master-Slave (pan-niewolnik).

|

|

Przeanalizujmy ten układ.

Przemysł elektroniczny produkuje gotowe układy scalone zawierające przerzutniki D flip flop wyzwalane zboczem dodatnim. Często przerzutniki te wyposaża się w dodatkowe dwa wejścia:

Dla wymienionych wejść obowiązują stany zabronione, jak dla przerzutnika RS (po prostu człon SLAVE jest zwykle realizowany jako przerzutnik RS).

Poniżej przedstawiamy układ scalony SN7474 zawierający dwa przerzutniki D flip flop wyzwalane zboczem narastającym (dodatnim) sygnału zegarowego C. W tabelce stanów kolorem czerwonym zaznaczyliśmy stan zabroniony sygnałów wejściowych.

|

SN7474 - dwa

przerzutniki D flip flop

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

Z przerzutnika D wyzwalanego zboczem można w prosty sposób uzyskać tzw. przerzutnik T (ang. Toggle = Zmiana). Przerzutnik T przy każdym ujemnym zboczu sygnału zegarowego (przejściu ze stanu 1 do stanu 0) zmienia stany wyjść na przeciwne.

| Przerzutnik T z przerzutnika D |

Zbudujemy teraz przerzutnik T z przerzutnika D typu SN7474. Układ aplikacyjny będzie następujący:

|

SN7474 - dwa

przerzutniki D flip flop

|

Spis elementów:

| Element | Ilość | Opis |

| zasilacz 5V | 1 | do zasilania elementów elektronicznych |

| płytka stykowa + kable | 1 | do montażu elementów elektronicznych |

| SN7474 | 1 | 2 przerzutniki D wyzwalane zboczem dodatnim |

| opornik 1kΩ/0,125W | 2 | –( )– do podłączania wejść bramek do +5V |

| opornik 120Ω/0,125W | 1 | –( )– do ograniczania napięcia i prądu diody LED |

| czerwona dioda LED | 1 | do sygnalizacji stanu wysokiego na wyjściu Q przerzutnika |

| mikroprzełącznik | 1 | do zmiany stanu logicznego wejścia C |

Gdy naciśniesz przycisk, to na wejście zegarowe C przerzutnika D zostanie podany stan logiczny 0. Gdy teraz zwolnisz ten przycisk, przerzutnik przepisze stan wejścia D na wyjście Q. Ponieważ wejście D jest połączone z wyjściem Q, to stan przerzutnika zawsze zmienia się na przeciwny.

Uwaga:

Przerzutniki typu T są stosowane w licznikach oraz w dzielnikach częstotliwości.

|

| I Liceum Ogólnokształcące |

Pytania proszę przesyłać na adres email: i-lo@eduinf.waw.pl

W artykułach serwisu są używane cookies. Jeśli nie chcesz ich otrzymywać,

zablokuj je w swojej przeglądarce.

Informacje dodatkowe