w I-LO w Tarnowie

Materiały dla uczniów liceum

|

Autor artykułu: mgr Jerzy Wałaszek

©2026 mgr Jerzy Wałaszek

|

Serwis Edukacyjny w I-LO w Tarnowie

Materiały dla uczniów liceum |

Autor artykułu: mgr Jerzy Wałaszek |

©2026 mgr Jerzy Wałaszek

|

| Podrozdziały |

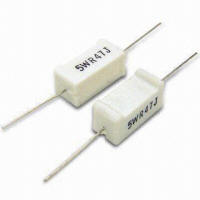

Opornik/rezystor:

|

|

|

Opornik jest elementem liniowym, dla którego obowiązuje prawo Ohma:

|

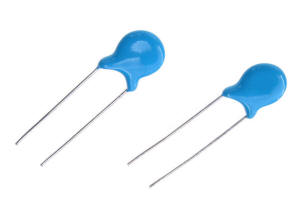

Kondensator:

|

|

|

W kondensatorze obowiązuje wzór:

|

Cewka:

|

|

|

Dla cewki obowiązuje wzór:

|

Dioda:

|

|

|

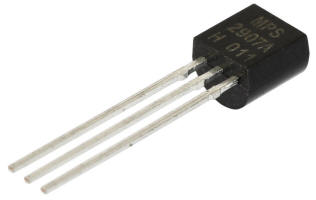

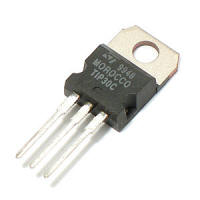

Tranzystor:

|

|

|

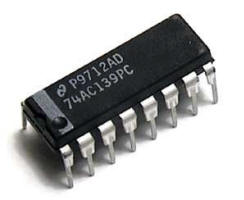

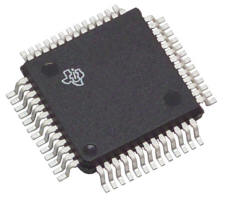

Układ scalony:

|

|

|

Elementy elektroniczne służą do tworzenia różnych układów elektronicznych, które spełniają odpowiednie funkcje (radioodbiornik, telewizor, odtwarzacz CD/DVD/BluRay, itp.).

Układy elektroniczne dzielimy na analogowe i cyfrowe. Analogowe przetwarzają sygnały o nieskończonej (ciągłej) liczbie poziomów. Układy cyfrowe ograniczają przetwarzane sygnały zwykle do dwóch poziomów:

Nazwa techniki cyfrowej wywodzi się właśnie stąd, iż poziom niski oznaczany jest cyfrą 0, a poziom wysoki cyfrą 1.

Układy cyfrowe opierają się na algebrze Boole'a. W algebrze tej używane są tylko dwa symbole: true i false dla oznaczenia odpowiednio prawdy i fałszu. Jeśli prawdzie przydzielimy cyfrę 1, a fałszowi cyfrę 0, to otrzymamy tzw. logikę dodatnią. Możliwy jest również przydział odwrotny, tzn. prawdzie przydzielamy 0, a fałszowi 1. Wtedy otrzymamy tzw. logikę ujemną.

|

Układ cyfrowy posiada pewną liczbę wejść oraz wyjść. Na wejściach mogą pojawiać się sygnały o dwóch stanach logicznych: 0 lub 1 (często oznacza sie je jako L i H od angielskich słówek Low, niski oraz High, wysoki). Na wyjściach pojawiają się również sygnały logiczne 0 lub 1, które powstają jako wynik funkcji spełnianej przez układ nad sygnałami wejściowymi. Przykładowo rozważmy element zwany bramką NOT.

|

|

Element ten posiada jedno wejście A i jedno wyjście Y. Na wyjściu Y pojawia się stan przeciwny logicznie do stanu panującego na wejściu A:

| A | Y |

| 0 | 1 |

| 1 | 0 |

Poziomy logiczne są reprezentowane w układach cyfrowych za pomocą odpowiednich napięć elektrycznych. Konkretne wartości tych napięć zależą od rodziny układów oraz od napięcia zasilającego. Jednakże zakresy napięć uznawanych za poziom niski i wysoki są zawsze od siebie oddzielone:

|

Rozróżniamy następujące poziomy napięć:

Układy cyfrowe pobierają różne prądy na swoich wejściach w zależności od panującego na nich stanu logicznego. Dlatego rozróżniamy dwa rodzaje prądów wejściowych:

Wyjście układu cyfrowego może dostarczyć różnych prądów w zależności od stanu logicznego. Zatem również rozróżniamy dwa rodzaje maksymalnych prądów wyjściowych.

Od wartości prądów wejściowych i wyjściowych zależy obciążalność wyjść elementów cyfrowych. Określa ona liczbę wejść innych elementów, które można podłączyć do wyjścia danego elementu. Jeśli przykładowo parametr ten wynosi 10, to do jednego wyjścia da się podłączyć tylko 10 wejść innych elementów. Przekraczanie tej liczby jest zwykle złym pomysłem. Większa liczba wejść obciąża bardziej wyjście, co może spowodować, iż przestanie ono pracować stabilnie. Problem ten dotyczy tylko niektórych serii układów cyfrowych, głównie tych, które są oparte o tranzystory bipolarne. Układy z tranzystorami polowymi posiadają zwykle bardzo duże oporności wejściowe i nie obciążają wyjść w takim stopniu (ich prądy IIL oraz IIH są bardzo małe). Obciążalność może sięgać setek lub tysięcy wejść. Tutaj barierą mogą okazać się pojemności i indukcyjności pasożytnicze, które pojawiają się w rozbudowanych sieciach logicznych.

Sygnał nie pojawia się na wyjściu układu natychmiast po zmianie stanu jego wejść. Musi upłynąć pewien krótki czas, zanim dane wejściowe zostaną przetworzone wewnątrz układu. Czas ten nazywamy czasem propagacji, czyli przejścia sygnałów wejściowych w wyjściowe. Współczee układy osiągają bardzo krótkie czasy propagacji, wynoszące kilka nanosekund. Rozróżnia się następujące czasy propagacji:

Opóźnienia sygnałów mogą powodować zakłócenia w pracy sieci logicznej, czyli tzw. hazardy. Polegają one na tym, że sygnały docierają z różnymi opóźnieniami do elementów sieci i tworzone są chwilowo błędne stany wyjściowe. Dla przykładu rozważmy prostą sieć zbudowaną z dwóch bramek: NOT i OR.

|

|

|

||||||||||||||||||||||

|

Y = NOT A

|

Y = A OR B

|

Bramka OR realizuje funkcję alternatywy logicznej swoich sygnałów wejściowych. Na wyjściu panuje stan 1, jeśli stan 1 jest na jednym z jej wejść.

Poniższy układ bramek realizuje funkcję Y = (NOT A) OR B:

|

|||||||||||||||

|

Y = (NOT A) OR B

|

Jak widać, na wyjściu Y otrzymujemy stan 0, jeśli wejście A ma stan 1, a wejście B stan 0. W każdym innym przypadku wyjście Y ma stan 1. Tak jest w teorii. Spójrzmy jednak na poniższą sieć logiczną:

|

Poniżej na wykresie przedstawiono przebiegi czasowe sygnałów. Załóżmy, że czerwone linie pionowe odpowiadają czasom propagacji sygnału przez bramki (i dodatkowo zakładamy, że czasy propagacji są sobie równe, co w praktyce jest raczej trudne do osiągnięcia). W momencie 1 sygnały wejściowe przyjmują kombinację stanów, dla której na wyjściu Y powinno pojawić się 0. Sygnały te utrzymują się przez czas propagacji i w chwili 2 powracają z powrotem do stanu wyjściowego. Co dzieje się na wyjściu? Otóż nic. Układ jakby przeoczył tę zmianę stanów wejściowych. Dlaczego? Z powodu propagacji sygnału przez bramkę NOT zmiana sygnału A dociera do punktu A' dopiero po czasie propagacji. Jednakże w tym czasie sygnał B powraca do stanu wysokiego. Zatem na wejściach bramki OR cały czas panuje sytuacja, gdy jeden z jej sygnałów wejściowych ma stan 1, zatem wyjście Y cały czas przyjmuje stan 1.

Jak widzimy, układ ten dla tej konkretnej sytuacji nie zachowuje się poprawnie. To właśnie nazywamy hazardem. Oczywiście, gdyby zmiana sygnałów wejściowych trwałaby dłużej niż czas propagacji, to stan tej sieci ustaliłby się i na wyjściu Y pojawiłby się stan niski 0.

Hazardy są zjawiskiem powszechnym w sieciach. Można z nimi walczyć, lecz jest to zadanie bardzo trudne, gdyż rolę odgrywają tutaj parametry poszczególnych elementów sieci, a te mogą posiadać różne rozrzuty produkcyjne. Dlatego w sieciach wprowadza się tzw. taktowanie. Stan sieci jest odczytywany nie w sposób ciągły, lecz w odpowiednio dobranych odstępach czasowych (taktach zegarowych), które zapewniają ustalenie się stanów logicznych na poszczególnych komponentach sieci. Im krótsze czasy propagacji elementów, tym szybciej może być taktowana sieć.

Wejścia niewykorzystane nie powinny pozostawać niepodłączone, gdyż prowadzi to do pogorszenia parametrów elementu cyfrowego. Istnieje kilka możliwości rozwiązania problemu tych wejść. Najprościej jest połączyć je z wejściem wykorzystanym, lecz wtedy zwiększa się obciążenie wyjścia układu sterującego (istotne w układach z tranzystorów bipolarnych). Jeśli mamy zapas, to rozwiązanie takie jest jak najbardziej wskazane. Jeśli wejście niepodłączone powinno być w stanie niskim, to podłączamy je do masy, a jeśli w stanie wysokim, to podłączamy je do napięcia zasilającego (o ile nie przekracza ono 5,5V, inaczej należy zastosować opornik co najmniej 1kΩ).

|

|

|

|

| Łączenie wejść ze sobą |

Do masy | Do plusa zasilania |

Do plusa zasilania przez opornik |

Ostatnim omawianym tutaj parametrem jest zakres temperatur pracy TA. Określa on, w jakich temperaturach może pracować dany układ. Przekroczenie tych wartości objawia się zwykle niestabilna pracą układu lub prowadzi do jego uszkodzenia. Temperatura pracy wpływa również na pozostałe parametry układu, np. jej wzrost wydłuża czasy propagacji. Dokładne dane znajdziesz w materiałach producentów, które są dostępne w sieci, niestety, w większości w języku angielskim (co powinno zmotywować cię do jego nauki).

| Parametr | Opis | 54 | 74 | 74S | 74LS | 74AC | 74ACT | 74HC | 74HCT | Jedn. |

| VCC | Napięcie zasilające | 4,5–5,5 | 4,75–5,25 | 2–6 | 4,5–5,5 | 2–6 | 4,5–5,5 | V | ||

| VOL | Niski poziom na wyjściu | 0,2–0,4 | 0,5 | 0,24–0,4 | 0,1 | 0,1–0,4 | V | |||

| VOH | Wysoki poziom na wyjściu | 2,4–3,4 | 2,7–3,4 | 0,9VCC | V | |||||

| IOL | Prąd wyjścia w stanie niskim | 16 | 20 | 8 | 75 | 25 | mA | |||

| IOH | Prąd wyjścia w stanie wysokim | -0,4 | -1 | -0,4 | -75 | -25 | mA | |||

| VIL | Niski poziom na wejściu | 0,8 | 0,5VCC | 0,8 | 0–0,25VCC | V | ||||

| VIH | Wysoki poziom na wejściu | 2 | 0,7VCC | 2 | 0,54VCC | V | ||||

| IIL | Prąd wejścia w stanie niskim | 1,6 | 2 | 0,4 | 0,1–1µA | mA | ||||

| IIH | Prąd wejścia w stanie wysokim | 40 | 50 | 20 | 0,1 | µA | ||||

| tp | Średni czas propagacji bramki | 9–18 | 3–5 | 9–15 | 1,5–8 | 7 | 10 | ns | ||

| TA | Zakres temperatur pracy | -55–125 | 0–70 | -40–85 | -40–125 | °C | ||||

| v | |||||

| 74 | 74H | 74L | 74S | 74LS | |

| 74 | 10 | 8 | 40 | 8 | 20 |

| 74H | 12 | 10 | 50 | 10 | 25 |

| 74L | 2 | 1 | 20 | 1 | 10 |

| 74S | 12 | 10 | 100 | 10 | 50 |

| 74LS | 5 | 4 | 40 | 4 | 20 |

Powyższa tabelka przedstawia obciążalność wyjść układów określonego wykonania TTL, które sterują układy o innym wykonaniu. Na przykład wyjście bramki TTL typu 74Lxx może wysterować tylko 2 wejścia typowego układu 74xx, a 1 wejście układów typu 74Hxx i 74Sxx. Przekroczenie tych parametrów spowoduje niestabilną pracę sieci.

| Symbol | Funkcja |

|

|

Bufor wzmacniający, nie zmienia stanu sygnału |

|

|

Negacja, NIE, NOT |

|

|

Suma logiczna, alternatywa, LUB, OR |

|

|

Iloczyn logiczny, koniunkcja, I, AND |

|

|

Zaprzeczona suma logiczna, NIE–LUB, NOR |

|

|

Zaprzeczony iloczyn logiczny, NIE–I, NAND |

|

|

Suma modulo 2, WYŁĄCZNIE–LUB, EXCLUSIVE OR |

|

|

Zaprzeczona suma modulo 2, WYŁĄCZNIE–NIE–LUB, EXCLUSIVE NOR |

|

Przerzutnik typu JK (master slave) wyzwalany zboczem ujemnym |

|

Przerzutnik D typu Latch wyzwalany poziomem wysokim |

|

Przerzutnik typu D wyzwalany zboczem ujemnym |

Przerzutniki oraz inne układy cyfrowe są wyzwalane sygnałami zegarowymi. Istnieje kilka rodzajów takiego wyzwalania. Wyzwalanie poziomem oznacza, że element uaktywnia się (reaguje na zmiany stanu wejść), gdy wejście zegarowe przyjmuje określony poziom (niski lub wysoki). Wyzwalanie zboczem polega na tym, iż stan wejść oddziałuje na układ tylko w bardzo krótkim czasie, gdy sygnał zegarowy zmienia poziom logiczny. Zbocze dodatnie występuje wtedy, gdy zmiana następuje od stanu niskiego do wysokiego. Zbocze ujemne to zmiana odwrotna, od stanu wysokiego do niskiego.

| Oznaczenie | Działanie |

|

|

Wyzwalanie wysokim poziomem sygnału zegarowego C |

|

|

Wyzwalanie niskim poziomem sygnału zegarowego C |

|

|

Wyzwalanie dodatnim zboczem (0 → 1) sygnału zegarowego C |

|

|

Wyzwalanie ujemnym zboczem (1 → 0) sygnału zegarowego C |

Rodzina TTL posiada następujące oznaczenia:

Pole producent zawiera informacje o wykonawcy układu lub typie układu (różne firmy stosują tutaj różne systemy oznaczeń). Pierwsze układy TTL pojawiły się w roku 1961. Wyprodukowała je firma Texas Instruments, dlatego tradycyjnie rodzinę TTL oznacza się symbolem .

| brak | Różni producenci, np. Fairchild Semiconductor, STMicroelectronics, Philips | |

| CD | Haris | |

| IN | Integral Corp. | |

| M | STMicroelectronics | |

| MC | Motorola | |

| SL | System Logic Semiconductor | |

| SN | Texas Instruments | |

| TC | Toshiba Semiconductor | |

| UCY UCA |

CEMI, Polska, elementy historyczne. UCY

jest kodem: U – układ bipolarny (M – układ unipolarny) C – cyfrowy Y – profesjonalny (A – wojskowy) |

Pole seria:

| 74 | seria podstawowa | |

| 64 | seria wojskowa produkowana przez CEMI, odpowiednik 54 | |

| 54 | seria wojskowa o rozszerzonym zakresie temperatur pracy |

Pole wykonania określa sposób wykonania układu. W sieci logicznej w zasadzie powinny współpracować układy wykonane w tej samej technologii. Przy układach cyfrowych CMOS, które mają współdziałać z układami TTL bipolarnymi, należy zwrócić uwagę, czy ostatnią literką jest T, które oznacza kompatybilność na poziomie sygnałów ze standardem TTL, np. ACT lub HCT. Poniżej przedstawiono niektóre z oznaczeń.

| brak | wykonanie standardowe z tranzystorów bipolarnych | |

| L | Low power, niski pobór mocy | |

| H | High speed, wysoka prędkość działania | |

| S | Shottky, wersja szybka | |

| AS | Advanced Shottky. ulepszona wersja S o większej szybkości | |

| LS | Low power Shottky, niski pobór mocy przy dużej szybkości | |

| ALS | Advanced Low power Shottky, ulepszona wersja LS | |

| F | Fast, wersja szybka | |

| C | CMOS, wykonanie z tranzystorów polowych | |

| HC | High speed CMOS, wersja szybka na tranzystorach polowych | |

| HCT | Wersja HC, kompatybilna z TTL | |

| AC | Advanced CMOS, wersja szybsza od S, a wolniejsza od F | |

| ACT | Wersja AC kompatybilna z TTL | |

| LV | Low Voltage, niskie napięcie zasilania, 2...5V | |

| VH | Very High speed, bardzo duża szybkość działania | |

| VHC | Very High speed CMOS, bardzo szybka prędkość działania w technologii CMOS |

Pole typu układu określa rodzaj spełnianych przez niego funkcji. Na przykład 00 to cztery bramki NAND.

Pole obudowa. Określa rodzaj zastosowanej obudowy (producenci stosują tutaj własne oznaczenia), np.:

| N | DIP, wyprowadzenia po obu bokach obudowy |

Układy podstawowej serii TTL wyszły dzisiaj już z użycia i praktycznie nikt ich nie produkuje. Zastępują je układy wykonane w technologii polowej CMOS, np. seria HCT i ACT. Seria CMOS pobiera mniej energii, jest dużo szybsza i działa stabilniej w większym zakresie temperatur. Układy te są kompatybilne z serią TTL co do końcówek oraz poziomów napięć logicznych. Wynika z tego, że zamiast np. układu 7404N (którego raczej już nigdzie nie kupisz) możesz z powodzeniem zastosować układ 74HCT04 lub podobny.

| Symbol | Nazwa | Opis |

| VCC | Napięcie zasilania | Jest to napięcie przyłożone pomiędzy końcówki VCC (plus zasilania) i GND (masa układu) w układzie scalonym. Dla serii standardowej TTL 74xx napięcie to mieści się w granicach od 4,75V do 5,25V. |

| ICC | Prąd zasilania | Jest to prąd wpływający do końcówki VCC (plus zasilania) układu cyfrowego. |

| ICCL | Prąd zasilania w stanie niskim | Jest to prąd wpływający do końcówki VCC (plus zasilania) układu cyfrowego, gdy na wyjściu panuje stan niski 0 (L – low). |

| ICCH | Prąd zasilania w stanie wysokim | Jest to prąd wpływający do końcówki VCC (plus zasilania) układu cyfrowego, gdy na wyjściu panuje stan wysoki 1 (H – high). |

| Ptot | Całkowita moc tracona | Jest to moc, którą pobiera z zasilacza dany układ cyfrowy |

| Symbol | Nazwa | Opis |

| VI | Napięcie wejściowe | Jest to napięcie, które przykłada się do wejścia elementu logicznego. |

| VIM | Maksymalne napięcie wejściowe | |

| VImin | Minimalne napięcie wejściowe | |

| -VI | Ujemne napięcie wejściowe | Jest to napięcie wejściowe, które posiada ujemną polaryzację w stosunku do masy układu. Napięcie to określa się dla ustalonej wartości prądu wejściowego. Jest to napięcie przewodzenia diod ograniczających. |

| VIL | Napięcie wejściowe w stanie niskim | Jest to napięcie przyłożone do wejścia układu, które określa niski poziom logiczny 0 (L – low). Wartość maksymalna tego napięcia dla układów TTL jest równa 0,8V. |

| VIH | Napięcie wejściowe w stanie wysokim | Jest to napięcie przyłożone do wejścia układu, które określa wysoki poziom logiczny 1 (H – High). Minimalna wartość tego napięcia dla układów TTL jest równa 2V. |

| VT+ | Napięcie progowe zbocza narastającego | Jest to poziom napięcia wejściowego, dla którego napięcia wejściowe i wyjściowe stają się równe przy narastaniu napięcia wejściowego od poziomu poniżej VT-. |

| VT- | Napięcie progowe zbocza opadającego | Jest to poziom napięcia wejściowego, dla którego napięcia wejściowe i wyjściowe stają się równe przy opadaniu napięcia wejściowego od poziomu powyżej VT+. |

| II | Prąd wejściowy | Jest to prąd wpływający do wejścia elementu logicznego. |

| -II | Ujemny prąd wejściowy | Jest to prąd wypływający z wejścia elementu logicznego, jeśli zostanie ono spolaryzowane ujemnie. Prąd ten jest głównie prądem przewodzenia diod ograniczających, którymi są zabezpieczane wejścia. |

| IIL | Prąd wejściowy w stanie niskim | Jest to prąd wpływający do wejścia układu cyfrowego przy wysterowaniu go maksymalnym napięciem dla stanu niskiego 0 (dla TTL 0,8V). |

| IIH | Prąd wejściowy w stanie wysokim | Jest to prąd wpływający do wejścia układu cyfrowego przy wysterowaniu go minimalnym napięciem dla stanu wysokiego 1 (dla TTL 2V). |

| n | Obciążenie wnoszone przez wejście | Obciążenia należy rozpatrywać w obrębie układów danej serii, np 74LSxx. W przeciwnym razie należy korzystać z tabelek przeliczeniowych. Dla wejść bramek cyfrowych obciążenie wynosi standardowo 1. Inne układy cyfrowe (przerzutniki, rejestry, multipleksery) mogą posiadać wejścia o większym obciążeniu, ponieważ wewnątrz dane wejście może być podłączone do wejść kilku bramek. |

| Symbol | Nazwa | Opis |

| VO | Napięcie wyjściowe | Jest to napięcie pojawiające się na wyprowadzeniu wyjściowym układu cyfrowego. |

| VOL | Napięcie wyjściowe w stanie niskim | Jest to napięcie pojawiające się na wyjściu układu cyfrowego i określające dla niego stan niski 0 (L – low). Napięcie to jest mierzone dla ustalonego prądu wyjściowego IOL. Dla standardowej serii TTL napięcie to wynosi 0,4V, a dla serii szybkiej 0,5V. |

| VOH | Napięcie wyjściowe w stanie wysokim | Jest to napięcie pojawiające się na wyjściu układu i określające dla niego stan wysoki 1 (H – high). Napięcie to jest mierzone dla ustalonej wartości prądu wyjściowego IOH. Gwarantowana wartość tego napięcia dla serii standardowej TTL wynosi 2,4V, a dla serii szybkiej 2,7V. |

| IO | Prąd wyjściowy | Prąd płynący do wyjścia elementu. |

| IOL | Prąd wyjściowy w stanie niskim | Jest to prąd płynący do wyjścia układu cyfrowego, dla którego zostaje na tym wyjściu zachowane napięcie odpowiadające poziomowi niskiemu 0 (L – low). Dla układów TTL prąd wyjściowy IOL jest dużo większy od prądu wejściowego IOH. Istotne staje się to przy sterowaniu innych elementów niż wejścia układów cyfrowych tej samej serii (np. diody LED). |

| IOH | Prąd wyjściowy w stanie wysokim | Jest to prąd płynący do wyjścia układu cyfrowego, dla którego zostaje na tym wyjściu zachowane napięcie odpowiadające poziomowi wysokiemu 1 (H – high). Oznacza się go wartością ujemną, ponieważ faktycznie płynie on w kierunku odwrotnym. |

| IOS | Zwarciowy prąd wyjściowy | Jest to prąd płynący do wyjścia układu cyfrowego znajdującego się w stanie wysokim, gdy wyjście to zostanie zwarte z masą. |

| NL | Obciążalność w stanie niskim | Jest to liczba wejść standardowych, które można sterować z danego wejścia znajdującego się w stanie niskim 0. |

| NH | Obciążalność w stanie wysokim | Jest to liczba wejść standardowych, które można sterować z danego wejścia znajdującego się w stanie wysokim 1. |

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.