w I-LO w Tarnowie

Materiały dla uczniów liceum

Wyjście Spis treści Wstecz Dalej

Autor artykułu: mgr Jerzy Wałaszek

©2026 mgr Jerzy Wałaszek

|

Serwis Edukacyjny w I-LO w Tarnowie

Materiały dla uczniów liceum |

Wyjście Spis treści Wstecz Dalej

Autor artykułu: mgr Jerzy Wałaszek |

©2026 mgr Jerzy Wałaszek

|

| SPIS TREŚCI |

| Podrozdziały |

Najprościej mówiąc bramka logiczna jest urządzeniem, które przetwarza bity wejściowe dając w wyniku bit wynikowy, którego wartość jest pewną funkcją logiczną wartości bitów wejściowych. W technice cyfrowej bity przedstawiane są najczęściej poziomem napięcia. Jeśli poziom ten zawiera się w zakresie od 0,4...0,8V, to mamy do czynienia ze stanem niskim L lub 0. Poziom od 2,0...2,4..5V oznaczamy jako H lub 1. Są to tzw. poziomy logiczne. Napięcia takie doprowadza się do wejść bramek. Na wyjściu bramki otrzymuje się napięcie 0,4V (L - 0) lub 2,4V (H - 1), które jest funkcją logiczną doprowadzonych do jej wejść poziomów logicznych. W logice obowiązują tylko dwie wartości - 0 (tzw. fałsz - ang. false) oraz 1 (tzw. prawda - ang. true). Wartości te mogą być bezpośrednio przedstawiane przy pomocy bitów.

Do konstrukcji nawet najbardziej złożonych układów cyfrowych (np. mikroprocesor) konieczne są trzy podstawowe elementy logiczne: NOT, AND oraz OR i jeden element pamięciowy, zwany przerzutnikiem. Przy omawianiu bramek będziemy stosować oznaczenia 0 dla poziomu L (0,4V) oraz 1 dla poziomu H (2,4V). O ile nie będziesz konstruował układów cyfrowych, wartość tych napięć nie jest dla ciebie specjalnie istotna.

| a | NOT a a |

| 0 | 1 |

| 1 | 0 |

Bramka NOT (pol. NIE) jest najprostszą z bramek. Służy do odwracania poziomu 0 na 1 oraz 1 na 0. Z uwagi na tę funkcję nazywa się ją często INWERTEREM (czyli odwracaczem). Bramka ta realizuje logiczną funkcję NEGACJI, zwaną również ZAPRZECZENIEM. Obok przedstawiamy tabelkę wartości funkcji logicznej NOT. Poniżej natomiast jest model bramki NOT, z którym możesz sobie poeksperymentować (analogiczne modele mają pozostałe bramki logiczne). Symbol bramki to trójkąt. Na wyjściu jest kółko, które symbolizuje zaprzeczenie. Klikając myszką w kwadracik wejściowy powodujesz zmianę poziomu napięcia wejściowego (światełko zgaszone - 0, zapalone - 1). W odpowiedzi bramka ustawia właściwy poziom napięcia wyjściowego.

Bramka NOT

W logice negację zapisujemy jako kreseczkę ponad argumentem: a - normalnie, a - zaprzeczone a.

| a | b | a AND b a · b |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Bramka AND (pol. I) jest dwuwejściowa (produkowane są również bramki AND o 3, 4 i 8 wejściach, ale to na razie nie musi cię wcale martwić). Oznacza to, iż doprowadzamy do niej dwa sygnały wejściowe, które dla wygody oznaczyliśmy sobie literkami a i b. Poziom logiczny wyjścia bramki AND zależy od poziomów logicznych na obu wejściach. Tabelka po lewej stronie pokazuje nam, jaki poziom będzie na wyjściu bramki (a AND b), gdy na wejściach podana zostanie odpowiednia kombinacja bitów. Wynika z niej, że na wyjściu otrzymamy stan 1 (czyli 2,4V), gdy na obu (w przypadku bramek AND wielowejściowych - na wszystkich) wejściach będzie równocześnie też stan 1. W przeciwnym razie wyjście bramki przyjmie stan 0 (0,4V). Bramka AND realizuje tzw. ILOCZYN logiczny, zwany także KONIUNKCJĄ. W logice koniunkcję zapisujemy za pomocą znaku kropki mnożenia lub pomijamy: a · b - koniunkcja a i b. Zwróć uwagę na podobieństwo wartości funkcji logicznej AND do mnożenia przez 0 i 1.

Bramka AND

| a | b | a OR b a + b |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Bramka OR (pol. LUB) jest również dwuwejściowa (podobnie jak w przypadku bramki AND produkowane są bramki OR o 3, 4 i 8 wejściach). Na wyjściu tej bramki będzie stan 1, gdy na którymkolwiek z wejść pojawi się stan 1. Wyjście przyjmie stan 0, gdy na wszystkich wejściach będzie również stan 0.

Bramka OR realizuje tzw. SUMĘ logiczną, zwaną również ALTERNATYWĄ. W logice alternatywę zapisujemy znakiem dodawania: a + b. Zwróć uwagę na podobieństwo funkcji logicznej OR do sumowania 0 i 1. Różnica występuje pozornie w przypadku, gdy oba argumenty są równe 1. Przyjmij jednak, iż jedynka logiczna nie jest liczbą, lecz informacją typu - coś większe od zera. Przy takim podejściu suma logiczna przestaje być dziwna: coś większe od zera plus coś większe od zera daje w wyniku coś większe od zera.

Bramka OR

W logice cyfrowej bardzo ważną rolę pełnią prawa rachunku logicznego. Podobnie jak w zwykłej algebrze, również w logice obowiązują różne zasady pozwalające przekształcać wyrażenia logiczne. Dzięki nim możemy upraszczać wyrażenia złożone oraz dokonywać rachunku logicznego.

Podstawowe prawa DeMorgana dotyczą zaprzeczenia sumy i iloczynu logicznego. Zapisujemy je następująco:

|

Prawo pierwsze: a + b = a · b |

| a | b | a + b | a + b | a | b | a · b |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 |

Prawo to mówi, iż zaprzeczenie sumy logicznej równe jest iloczynowi zaprzeczeń każdego z argumentów. Dowód logiczny można przeprowadzić za pomocą tabelki wartości argumentów i funkcji logicznych. tabelki takie noszą nazwę tablic prawdy (ang. truth tables). W oznaczonych kolumnach obliczyliśmy odpowiednio zaprzeczenie sumy argumentów a i b oraz iloczyn zaprzeczeń a i b. Kolumny te zawierają identyczne wartości logiczne, co dowodzi prawdziwości tego twierdzenia. Poniżej przedstawiam model prawa DeMorgana zrealizowany z podstawowych bramek AND, OR i NOT. Jeśli w obu układach ustawisz identyczną kombinację poziomów logicznych na wejściach bramek, to na wyjściu otrzymasz ten sam stan logiczny.

Prawa DeMorgana

|

Prawo drugie: a · b = a + b |

| a | b | a · b | a · b | a | b | a + b |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 |

Drugie prawo mówi, iż zaprzeczenie iloczynu logicznego równe jest sumie logicznej zaprzeczeń argumentów. Zwróć uwagę na symetrię tych praw. Obok przedstawiam tabelkę z dowodem prawdziwości równania DeMorgana.

Powyższe dwa prawa wprowadził do logiki Augustus DeMorgan (1806 - 1876), który wraz z drugim sławnym matematykiem, George'em Boole'em, stworzyli podstawy współczesnej logiki matematycznej będącej podstawą działania wszelkich układów cyfrowych, a więc również i komputerów.

|

| George Boole (1835-1882) |

Wykonywanie rachunków logicznych nie jest możliwe bez odpowiedniego aparatu matematycznego. Aparat taki opracował matematyk George Boole. To właśnie dzięki jego pionierskim pracom możesz dzisiaj cieszyć się z komputera stojącego na twoim biurku. Bez logiki nie ma komputerów. Na Algebrze Boole'a opiera się działanie sieci logicznych, które tworzą mikroprocesory i układy im towarzyszące. Programy komputerowe wykorzystują jej zasady i twierdzenia przy podejmowaniu różnych decyzji. Opisane poprzednio bramki logiczne dokonują podstawowych działań zgodnie z założeniami tej algebry. Dlatego poznanie jej jest jednym z priorytetowych celów przy nauce informatyki. W równaniach Algebry Boole'a będę konsekwentnie stosował opisaną przy bramkach logicznych notację dla podstawowych operacji:

| a + b | - suma logiczna, alternatywa |

| a · b | - iloczyn logiczny, koniunkcja |

| a | - zaprzeczenie logiczne, negacja |

W literaturze można spotkać również inne notacje, w zależności od tego, czy algebra Boole'a stosowana jest do wyrażeń logicznych, czy do zbiorów.

| a · 0 = 0 |

| a + 0 = a |

| a · 1 = a |

| a + 1 = 1 |

| a · a = a |

| a + a = a |

| a · a = 0 |

| a + a = 1 |

Oto lista trywialnych praw Algebry Boole'a (dowód tych praw wynika bezpośrednio z własności operacji logicznych negacji, koniunkcji oraz alternatywy). Jeśli myślisz, że te proste prawa nie mają wielkiego zastosowania w technice cyfrowej, to bardzo się mylisz. Oto odpowiedni przykład.

Z prawa a · 1 = a wynika, iż na nieużywane wejścia bramek AND można podać stan logiczny 1, a funkcja bramki nie ulegnie zmianie. Skąd biorą się nieużywane wejścia? To proste. Wyobraź sobie, iż do konstrukcji twojej sieci potrzebne są np. 3 bramki AND o 4 wejściach oraz jedna bramka AND o trzech wejściach. W układzie scalonym SN74LS21 umieszczone są dwie bramki AND o czterech wejściach. Układów takich potrzebujesz więc dwa. W sumie masz 4 bramki AND czterowejściowe. Potrzebujesz tylko trzech więc jedna pozostanie wolna. Możesz teraz zakupić układ SN74LS11, który zawiera trzy bramki AND o trzech wejściach każda. Jednak tutaj pozostaną dwie niewykorzystane. Prościej będzie zastosować w twojej sieci zamiast bramki trójwejściowej niewykorzystaną bramkę 4 wejściową. Ponieważ wejść bramek raczej nie powinno się ze sobą łączyć (zwiększa to obciążenie układów, z których bramka pobiera sygnał oraz może wpłynąć na wadliwą pracę sieci logicznej), to niepotrzebne wejście łączymy z poziomem napięcia o wartości ponad 2V i otrzymujemy bramkę trójwejściową.

| ā = a |

| a · b = b · a |

| a + b = b + a |

| a · (b + c) = a · b + a · c |

| a + (b · c) = (a + b) · (a + c) |

| a · (b · c) = (a · b) · c |

| a + (b + c) = (a + b) + c |

| a + a · b = a |

| a ·(a + b) = a |

| a · (a + b) = a · b |

| a + a · b = a + b |

| a + a · b = a + b |

| a + a · b = a + b |

| a + b = a · b |

| a · b = a + b |

A teraz przedstawiam listę mniej trywialnych praw Algebry Boole'a. Każde z nich można dowieść za pomocą tabel prawdy, jak zrobiliśmy to przy prawach DeMorgana lub wyprowadzić z pozostałych praw. Prawa Algebry Boole'a są bardzo pomocne przy upraszczaniu złożonych wyrażeń logicznych. Niektóre z nich bardzo przypominają prawa zwykłej algebry, niektóre nie mają ścisłego odpowiednika. Dwa ostatnie prawa są prawami DeMorgana.

Dla przykładu wyprowadzimy jedno z nich:

a + a · b = ?

Przyjmijmy, że a = 0. Wtedy otrzymujemy:

0 + 0 · b = 0 + 0 = 0, czyli jest równe a.

Teraz niech a = 1:

1 + 1 · b = 1 + b = b + 1 = 1, czyli znów równe a.

Wobec powyższego wartość logiczna b nie wpływa na wartość tego wyrażenia, zależy ono jedynie od wartości logicznej a i jest jej równe. Wyprowadzenie reszty własności pozostawiam jako ćwiczenie dla czytelnika.

Należy uprościć następujące wyrażenie logiczne:

y = a · b + a · b + a · b

W obecnej postaci do zrealizowania tego wyrażenia potrzebna jest sieć 6 bramek logicznych:

Realizacja wyrażenia y =

a·b

+ a·b + a·b w postaci sieci

logicznej z bramek NOT, AND oraz OR

Spróbujmy uprościć to wyrażenie stosując podane prawa Algebry Boole'a:

a · b + a · b + a · b = a · b + a · (b + b) = a · b + a · 1 = a · b + a = a + b

Wyrażenie pierwotne udało się nam sprowadzić do postaci y = a + b. Teraz potrzebujemy tylko dwie bramki do naszej sieci, a pracuje ona identycznie jak poprzednia:

Ta sama sieć logiczna po dokonaniu minimalizacji funkcji logicznej

Dokonane przez nas uproszczenie nazywa się minimalizacją funkcji logicznej i stanowi jedno z podstawowych zagadnień techniki cyfrowej. Dzięki rachunkowi logicznemu można upraszczać złożone funkcje logiczne, co daje wymierne korzyści w postaci uproszczenia struktury sieci logicznej, mniejszej liczby bramek, mniejszego kosztu urządzenia wynikowego, zwiększenia niezawodności działania, zmniejszenia poboru energii itd.

Bardzo często spotykamy się z problemem, gdy znane są wszystkie argumenty

funkcji logicznej, znane są jej wartości, ale nie znamy jej postaci. Jeśli

zechcemy utworzyć sieć logiczną, która realizuje taką funkcję, to musimy znaleźć

jej postać.

| a | b | c | y(a,b,c) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Funkcję logiczną, której postaci nie znamy, zadamy za pomocą tabelki wartości. Sposób ten jest często stosowany przy projektowaniu sieci logicznej - wiemy, jakie postacie mogą przyjmować dane wejściowe oraz wiemy, jakie wartości powinna dla nich przyjmować funkcja logiczna, bo wynika to np. ze sposobu działania sieci logicznej w tym konkretnym urządzeniu.

Z tabelki wartości funkcji możemy przykładowo odczytać, iż dla a =1, b = 0 i c =0 funkcja y(a,b,c) = 1 - możemy to zapisać też tak: y(1,0,0) = 1, co jest konkretną wartością funkcji logicznej dla konkretnych wartości jej argumentów.

Przy określaniu postaci funkcji y będą nas interesować tylko te przypadki, w

których przyjmuje ona wartość logiczną 1. W tabelce odpowiednie wiersze

zaznaczyliśmy grubą czcionką. Skorzystamy tutaj z własności sumy logicznej i

napiszemy:

y(a,b,c) = y(0,0,0) +

y(0,0,1) + y(1,0,0) + y(1,1,0) + y(1,1,1)

Konkretne wartości funkcji możemy potraktować jako iloczyny logiczne argumentów, które dają w wyniku wartość 1, gdy argumenty a, b i c przyjmą stan, dla którego funkcja ma wartość 1:

y(0,0,0) = 1, więc y(0,0,0) = a · b · c

Wyrażenie to daje w wyniku wartość logiczną 1 tylko wtedy, gdy wszystkie

argumenty mają stan logiczny 0. W każdym innym przypadku wynikiem jest 0. Zasada

jest bardzo prosta. Jeśli argument ma mieć wartość 1, to przyjmujemy go bez

zmian w iloczynie, a jeśli ma mieć wartość 0, to bierzemy jego zaprzeczenie.

Otrzymamy więc kolejno:

y(0,0,0) = a · b · c

y(0,0,1) = a · b · c

y(1,0,0) = a · b · c

y(1,1,0) = a · b · c

y(1,1,1) = a · b · c

Teraz wyrażenia te łączymy w sumę logiczną i otrzymamy pierwszy wzór naszej

funkcji:

y(a,b,c) =

a ·

b ·

c +

a ·

b · c + a ·

b ·

c + a · b ·

c + a · b · c

Teraz wkraczają zasady Algebry Boole'a, które umożliwią nam uproszczenie tego

wyrażenia. Najpierw wyciągniemy przed nawias wspólne czynniki

a ·

b oraz a · b:

y(a,b,c) =

a ·

b ·(c

+ c) + a · b ·

c + a · b · (c

+ c)

Ponieważ c + c = 1, to

y(a,b,c) = a · b + a · b · c + a · b

y(a,b,c) = a · b + a · (b · c + b)

y(a,b,c) = a · b + a · (c + b)

y(a,b,c) = a · b + a · c + a · b

Uff, napracowaliśmy się. Niestety, tak wygląda klasyczne rozwiązanie tego typu problemu. Przy większej liczbie argumentów rachunek logiczny bardzo się komplikuje i łatwo może dojść do pomyłki.

Zachodzi zatem pytanie, czy do tego samego wyniku nie można dojść prostszą drogą. Odpowiedź znalazł Maurice Karnaugh i opisał w książce pt. "The Map Method for Synthesis of Combinational Logic Circuits". Sposób minimalizacji funkcji logicznej polega na tworzeniu tzw. mapy Karnaugh'a. Przedstawimy teraz kolejne kroki tworzenia takiej mapy.

obszar niebieski - a · b, c - pomijamy, gdyż zmienia się z 0 na 1.

obszar zielony - a · b, c znów pomijamy, gdyż zmienia się z 0 na 1.

obszar fioletowy - a ·

c, tym razem pomijamy b,

gdyż zmienia się z 1 na 0

Poszukiwana funkcja logiczna y(a,b,c) jest

sumą logiczną zaznaczonych obszarów, więc:

y(a,b,c) = a · b + a · b + a · c

Otrzymaliśmy identyczny wynik jak przy metodzie klasycznej. Zwróć uwagę, iż nie musieliśmy wcale przeprowadzać żadnych obliczeń logicznych - to jest właśnie podstawowa zaleta map Karnaugh'a - pozwalają one w sposób prawie automatyczny zminimalizować funkcję logiczną.

Pokażemy teraz praktyczny sposób wykorzystania tej wiedzy przy projektowaniu różnych układów cyfrowych.

Układ ten porównuje ze sobą dwa bity danych. Na wyjściu otrzymujemy wartość 1, gdy bity te są takie same (równe oba zero lub 1), a 0, gdy bity różnią się. W technice cyfrowej funkcja taka nosi nazwę EX-NOR (pol. równoważność) i jest realizowana specjalnie produkowaną bramką logiczną (SN74LS266). My jednak zrealizujemy ją za pomocą dostępnych bramek podstawowych.

Funkcja równoważności przyjmuje wartość 1, gdy a=0 i b =0, lub a=1 i b=1. Stąd można szybko uzyskać jej postać:

a EX-NOR b =

a

· b

+ a · b

Do zrealizowania sieci logicznej potrzebne będą dwie bramki

NOT (zaprzeczenie sygnałów a i b), dwie bramki

AND (iloczyn

a·b

oraz a·b) i jedna bramka

OR (suma iloczynów). Poniżej przedstawiamy model

tej sieci, który działa podobnie do modeli pojedynczych bramek zaprezentowanych

w poprzednich rozdziałach.

Sieć logiczna komparatora jednobitowego

Bramka równoważności EX-NOR

Porównanie słów wielobitowych będzie polegało na zastosowaniu odpowiedniej

liczby komparatorów jednobitowych. Poniżej przedstawiamy odpowiedni przykład

(komparatory produkowane są jako gotowe układy - SN74LS85):

Komparator 4-bitowy

Układ taki występuje jako element każdego procesora. Jego zadaniem jest

wykonywanie podstawowej operacji arytmetycznej - dodawania dwójkowego. Sumator

jednobitowy dodaje po jednym bicie każdego z argumentów. Jeśli argumenty mają

więcej bitów (co zwykle zawsze ma miejsce), to

dodawanie realizuje odpowiedni zespół współpracujących ze sobą sumatorów

jednobitowych.

Sumator jednobitowy

Sumator ten posiada trzy wejścia:

oraz dwa wyjścia:

| cn-1 | a | b | cn | y |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Sumowanie wykonujemy według zasad sumowania

dwójkowego. Obok przedstawiamy tabelkę stanów dla wszystkich możliwych

sygnałów wejściowych. Ponieważ mamy dwa sygnały wyjściowe, cn

i

y, to dla każdego z nich będziemy musieli ułożyć

odpowiednią funkcję logiczną. Oba sygnały wyjściowe zależą od sygnałów na

wejściu sumatora. Możemy więc zapisać:

cn = c(cn-1,a,b)

oraz

y - y(cn-1,a,b)

Zadanie sprowadza się zatem do znalezienia funkcji logicznych c(cn-1,a,b)

i y(cn-1,a,b). Znajdziemy je za pomocą map Karnaugh'a, które

przedstawiamy poniżej.

c(cn-1,a,b) = a · b + cn-1 · b + cn-1 · a = a · b + cn-1 · (a + b)

Sieć logiczna dla sygnału wyjściowego przeniesienia cn

wymaga czterech bramek:

Sieć logiczna dla sygnału wyjściowego cn

y(cn-1,a,b) = cn-1·a·b + cn-1·a·b + cn-1·a·b + cn-1·a·b = cn-1·(a·b + a·b) + cn-1·(a·b + a·b)

Gdy zauważymy, że podwyrażenie a·b + a·b jest negacją podwyrażenia a·b + a·b (w logice musisz być bardzo bystry i zauważać takie rzeczy), to możemy ostatecznie zapisać:

|

__________ y(cn-1,a,b) = cn-1 · (a · b + a · b) + cn-1 · (a · b + a · b) |

Sieć logiczna sumy y wymaga dziesięciu bramek bramek:

Sieć logiczna dla sygnału wyjściowego y

Aby otrzymać kompletny sumator, należy obie sieci logiczne połączyć w jedną sieć o trzech sygnałach wejściowych cn-1, a i b oraz o dwóch sygnałach wyjściowych cn i y. Wynik wygląda następująco:

Sieć logiczna pełnego sumatora jednobitowego

Przedstawiony układ potrafi sumować binarnie słowa jednobitowe. Jeśli chcemy sumować dłuższe słowa, to łączymy kaskadowo odpowiednią ilość sumatorów (w praktyce tego sposobu się nie stosuje z uwagi na małą szybkość pracy kaskadowych sumatorów - zamiast nich wymyślono sumatory równoległe, ale to temat na inną okazję).

Szeregowy sumator 4-bitowy zbudowany z sumatorów jednobitowych

W ten oto sposób można budować układy liczące. Układ ten dodaje 4-bitowe liczby binarne a i b. Wynik pojawia się na wyjściach y. Przeniesienie c3 można połączyć z wejściem c0 następnej kaskady - uzyskamy w ten sposób sumator 8-bitowy. W rzeczywistości sumatory są dostępne jako gotowe układy logiczne (np. SN74LS82 lub SN74LS83) - nie musimy ich budować z bramek. Jeśli dokładnie prześledziłeś ten przykład, to powinieneś zrozumieć sposób pracy takich elementów. Wygląda to skomplikowanie? To w takim razie wyobraź sobie, jak skomplikowany jest komputer, w którym sumator to zaledwie drobna cząstka rozległej sieci logicznej.

| Kod NBC | Kod Gray'a | ||||

| b2 | b1 | b0 | g2 | g1 | g0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 0 |

Transkoder jest układem, który przetwarza dane zapisane w jednym kodzie na inny kod . W tym wypadku zaprojektujemy sieć logiczną zmieniającą 3-bitowy naturalny kod binarny NBC na wyrazy w kodzie Gray'a. Sieć będzie posiadała 3 wejścia danych b2, b1 i b0, na które należy podać wartość binarną. Na trzech wyjściach sieci g2, g1 oraz g0 pojawi się wtedy odpowiedni wyraz kodu Gray'a.

Stan każdego wyjścia sieci logicznej jest funkcją stanów na wejściach. Możemy

więc zapisać:

g2 = g2(b2,b1,b0)

g1 = g1(b2,b1,b0)

g0

= g0(b2,b1,b0)

Zadanie nasze sprowadza się zatem do odnalezienia tych funkcji. Dokonamy tego przy pomocy odpowiednich map Karnaugh'a, z których odczytamy również ich postać.

g2(b2,b1,b0) = b2

g2(b2,b1,b0) = b2

g1(b2,b1,b0) =

b2 · b1

+ b2 · b1

g1(b2,b1,b0) =

b2 · b1

+ b2 · b1

g0(b2,b1,b0) =

b1 · b0

+ b1 · b0

g0(b2,b1,b0) =

b1 · b0

+ b1 · b0

W dwóch ostatnich funkcjach logicznych występują podobne wyrażenia typu

a·b

+

a·b.

Jest to negacja omówionej poprzednio funkcji logicznej równoważności

EX-NOR. Funkcja ta, zwana w logice cyfrowej

EX-OR

(pol. suma modulo dwa) lub nierównoważnością, przyjmuje

wartość 0, gdy oba argumenty są identyczne, a wartość 1, gdy są one różne.

Funkcję tę można zrealizować z podstawowych bramek lub zastosować gotowe bramki

typu EX-OR (np. SN74LS86).

Operację sumy modulo dwa oznacza się w logice cyfrowej za pomocą symbolu: a Å b.

Poniżej przedstawiamy sieć logiczną funkcji EX-OR

zbudowaną ze standardowych bramek oraz dla porównania bramkę

EX-OR.

Sieć logiczna funkcji sumy modulo dwa

Bramka realizująca funkcję logiczną nierównoważności

W naszej sieci funkcję EX-OR realizujemy za pomocą gotowych bramek, co znacznie uprości jej schemat.

Sieć logiczna transkodera z kodu NBC na kod Gray'a

W praktyce zamiast różnorodnych bramek stosuje się bramki uniwersalne, które realizują funkcje NOT-AND (NIE-I) albo NOT-OR (NIE-LUB). Z praw DeMorgana wynika, iż bramki takie pozwalają zrealizować funkcje podstawowe NOT, AND oraz OR, a skoro tak, to za ich pomocą można konstruować wszelkie sieci logiczne.

| a | b | NOT(a AND b) a · b |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Bramka NAND (NOT-AND - NIE-I) realizuje funkcję zaprzeczenia iloczynu logicznego. Na wyjściu otrzymujemy stan zero, gdy wszystkie wejścia mają stan 1. W przeciwnym wypadku na wyjściu jest zawsze stan 1. Jest to najpopularniejsza bramka uniwersalna (SN74LS00). Przy konstruowaniu sieci logicznych istnieje tendencja sprowadzania wszystkich funkcji do funkcji NAND. Dzięki czemu sieć zbudowana jest z jednolitych elementów, jest tańsza i lepiej wykorzystuje bramki zawarte w układach scalonych. Poniżej przedstawiamy model bramki NAND oraz przykłady realizacji podstawowych funkcji logicznych przy jej pomocy.

Bramka uniwersalna NAND

|

|

|

|

Każdą, dowolnie skomplikowaną funkcję logiczną da się przy pomocy Algebry Boole'a sprowadzić do postaci, w której występują tylko same operacje NAND. Dzięki temu sieć logiczna może się składać z jednorodnych elementów, co znacząco może wpłynąć na koszt konstrukcji. Oto odpowiedni przykład:

| f(a,b,c,d) = a·b + c·d + a·c = | _______________ a·b + c·d + a·c = |

___ ___ ___ a·b · c·d · a·c |

|

|

|

Obie powyższe sieci logiczne są sobie równoważne, chociaż zbudowano je z różnych elementów logicznych. |

|

| a | b | NOT(a OR b) a + b |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Bramka NOR (NOT-OR) realizuje funkcję zaprzeczenia sumy logicznej. Sygnał wyjściowy przyjmuje wartość 1 tylko wtedy, gdy wszystkie sygnały na wejściach mają stan 0. W każdym innym przypadku na wyjściu panuje stan 0. Jest to druga po NAND bramka uniwersalna (SN74LS02), przy pomocy której można budować dowolne sieci logiczne. Poniżej przedstawiamy model tej bramki oraz przykłady realizacji podstawowych funkcji logicznych.

Bramka uniwersalna NOR

|

|

|

|

Dotychczas zajmowaliśmy się idealnymi bramkami logicznymi, w których stan wyjścia jest funkcją logiczną stanów wejściowych. Rzeczywistość jest jednak okrutna. Każda bramka logiczna pracująca w dowolnej sieci ma pewną budowę wewnętrzną (składa się zwykle z kilku tranzystorów, diod i oporników). Elementy te nie pracują dowolnie szybko. Przeładowanie stanu na wyjściu bramki wymaga pewnego czasu, który nazywamy czasem propagacji sygnału przez bramkę. Czas propagacji jest bardzo krótki i wynosi kilka nanosekund (w szybkich procesorach osiąga on poziom pikosekund). W prostych sieciach nie odgrywa on większej roli. Jednak w sieciach złożonych, gdzie sygnały wędrują różnymi drogami, czasy propagacji wprowadzają różne opóźnienia w działaniu poszczególnych elementów sieci, co może prowadzić przy źle zaprojektowanej sieci logicznej do błędów w jej działaniu.

Rozważmy następującą, prostą sieć logiczną, którą zbudowano z rzeczywistych bramek logicznych.

Sieć ta realizuje funkcję logiczną:

f(a,b) = a · b + b = a + b + b = a + 1 = 1

Na wyjściu bramki OR powinien utrzymywać się stan 1 bez względu na stan wejść

a i b. Załóżmy, że tak jest przy stanie wejść a=1 i b=1. Obrazuje to poniższy

rysunek:

Teraz niech stan wejścia b zmieni się z 1 na 0. Powstanie sytuacja jak na

poniższym rysunku:

Na wyjściu bramki OR wciąż panuje stan 1, ponieważ

sygnał z wejścia, z uwagi na czas propagacji, nie został jeszcze przetworzony

przez bramkę. To samo dotyczy bramki AND. Propagację

zaznaczyliśmy zieloną strzałką. Dopiero po upływie kilku nanosekund na wyjściach

tych bramek ustali się właściwy poziom sygnału, który będzie funkcją logiczną

sygnałów wejściowych, co obrazuje poniższy rysunek.

Na wyjściu bramki AND jest już właściwy stan logiczny,

który musi być przetworzony przez bramkę NOT, co zajmie kolejne kilka

nanosekund. Zwróćmy uwagę, że na wyjściu bramki OR pojawił się stan 0, który

zgodnie z wzorem funkcji nie powinien tam być.

Bramka NOT ustaliła już sygnał na swoim wyjściu. Teraz

nowy stan wejść musi być przetworzony przez bramkę

OR, na której wyjściu wciąż utrzymuje się stan 0.

Bramka OR przetworzyła stan wejść i na jej wyjściu ustalił się wreszcie stan 1, zgodny z funkcją realizowaną przez tę sieć.

Opisana powyżej sytuacja nosi nazwę zjawiska hazardu. Polega ono na tym, iż stan sieci ustala się dopiero po pewnym czasie (po sumie czasów propagacji bramek przetwarzających dane). Zanim się to stanie, stan wyjść sieci nie jest określony żadną funkcją logiczną (nawet dwie identyczne sieci mogą się różnie zachowywać z uwagi na rozrzuty parametrów tworzących je bramek). Hazard stanowi podstawową trudność przy projektowaniu dużych i skomplikowanych sieci logicznych.

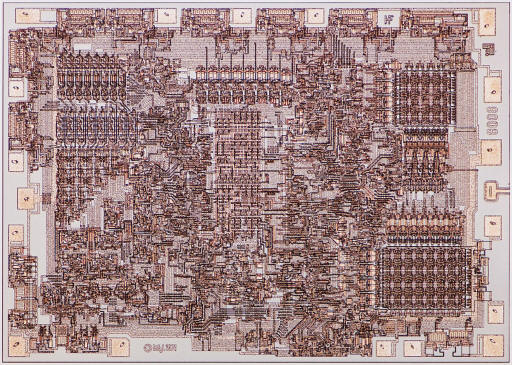

|

| Wnętrze układu mikroprocesora |

Jednym ze sposobów walki z hazardem jest wprowadzenie synchronizującego

sygnału zegarowego - tzw. taktowania. Sygnał zegarowy jest sygnałem cyfrowym

pulsującym z określoną częstotliwością pomiędzy stanami 0 i 1, zwykle kilkaset

MHz. Wszystkie elementy sieci synchronizują się do tego sygnału. Okres taktu

zegarowego musi być tak dobrany, aby w sieci zanikły hazardy i ustaliły się

sygnały wyjściowe bramek logicznych. Stan sieci jest następnie analizowany

przy końcu taktu zegarowego. Ze sposobu tego korzystają wszystkie współczesne

komputery - słynna częstotliwość taktowania procesora. Rozumiesz teraz, iż dla

danego układu cyfrowego nie można tej częstotliwości dowolnie zwiększać. Szybszy

procesor to również konieczność opracowania szybszej sieci logicznej o

mniejszych czasach propagacji sygnału na bramkach. Jeśli będziesz zwiększał

częstotliwość taktowania układu cyfrowego, to w końcu dojdziesz do punktu, w

którym jego sieć logiczna nie jest w stanie ustalić się w okresie taktu

zegarowego (wciąż będą w niej obecne hazardy) i po

prostu odmówi działania. Z drugiej strony bramka logiczna najwięcej energii

pobiera w trakcie zmiany swojego stanu na wyjściu (zmiana

napięcia wiąże się z przeładowaniem ładunków elektrycznych, a to oznacza krótki

impuls prądowy). Większa częstotliwość taktowania powoduje zwiększenie

liczby przełączeń w sieci logicznej, a tym samym wzrost pobieranej przez nią

energii, która zamieniana jest na ciepło. Jeśli układ nie będzie odpowiednio

chłodzony, to może dojść do jego przegrzania i w konsekwencji do zniszczenia

struktury półprzewodnikowej. W przypadku procesora jest to bardzo nieprzyjemne

zjawisko z punktu widzenia kieszeni użytkownika.

Zjawisko opóźnienia propagacji sygnału na bramce znajduje również szereg użytecznych zastosowań. Wykorzystując nieparzystą liczbę bramek odwracających (NOT, NAND lub NOR) można w prosty sposób zrealizować generator przebiegu prostokątnego (tzn. ciągów 1 i 0).

Generator sygnału prostokątnego

Częstotliwość takiego generatora zależy od sumy czasów propagacji tworzących go bramek. Nie jest ona idealnie stała, gdyż czas propagacji zależy również od temperatury pracy układu cyfrowego, ale w prostych zastosowaniach jest to rozwiązanie zupełnie wystarczające. Zwróć uwagę, iż nie istnieje funkcja logiczna opisująca stan wyjścia takiego układu - funkcja ta musiałaby jako argument brać samą siebie!

Kolejnym utrudnieniem przy projektowaniu dużych sieci logicznych jest obciążalność wyjść bramek. Każda bramka pobiera w trakcie pracy pewną energię z bramki, do której jest podłączona. Obciążalność określa, ile wejść bramek można połączyć z wyjściem bramki. Jeśli np. obciążalność wynosi 25, to do wyjścia bramki może jednocześnie być podłączonych 25 wejść innych bramek. Parametru tego nie wolno przekraczać, gdyż bramka zbytnio obciążona może nie pracować poprawnie (np. nie będzie w stanie wysterować wyjścia na odpowiedni poziom logiczny lub wzrośnie jej czas propagacji i sieć przestanie działać dla założonej częstotliwości taktowania albo po prostu się spali). Dlatego nieużywane wejścia bramek zaleca się raczej łączyć z masą (poziom logiczny 0) lub z plusem zasilania (poziom logiczny 1) niż ze wejściami używanymi.

Przerzutnik (ang. flip-flop) jest elementem logicznym, który ma cechę zapamiętywania informacji. Inaczej mówiąc, przerzutnik ma dwa stany stabilne. Najprostsze przerzutniki można budować z bramek logicznych. Bardziej zaawansowane wymagają odpowiednich rozwiązań układowych. Przerzutniki posiadają zwykle kilka wejść sterujących oraz dwa (czasem tylko jedno) wyjścia przeciwsobne, które oznaczamy Q i Q. Stan tych wyjść jest zawsze przeciwny.

Jest to najprostszy rodzaj przerzutnika. Posiada on dwa wejścia:

oraz dwa wyjścia Q i Q, na których występuje stan przeciwny.

Przerzutnik R-S może być wykonany z dwóch bramek NAND lub NOR. Działanie przerzutnika zależy od tworzących go bramek, ale w obu przypadkach można wskazać na podobieństwa. Poniżej omawiamy dokładnie oba przypadki.

| S | R | Qn |

| 1 | 1 | Qn-1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 0 | 0 | 1 |

W przypadku wykonania przerzutnika R-S z bramek NAND stanem aktywnym wejść jest stan 0, dlatego czasami przerzutnik taki oznacza się jako przerzutnik R-S. Gdy na wejściach R i S panuje stan 1, to przerzutnik pamięta swój poprzedni stan, oznaczony w tabelce jako Qn-1. Dlatego właśnie ten element logiczny nazywamy elementem pamięciowym. Jeśli wejście S zmieni swój stan na 0 (R wciąż musi mieć stan 1), to na wyjściu Q pojawi się stan 1. Mówimy, iż poziom niski na wejściu S ustawia wyjście Q na 1. Stąd oznaczenie tego wejścia literką S będącą skrótem angielskiego słowa Set (ustaw). Drugie wejście, R, pełni funkcję odwrotną. Pojawienie się niskiego poziomu na R (na S musi być 1) spowoduje ustawienie stanu 0 na wyjściu Q. Mówimy, iż poziom niski na wejściu R zeruje wyjście Q. Stąd pochodzi oznaczenie wejścia literką R od angielskiego słowa Reset (zeruj).

Problem pojawia się, gdy jednocześnie na obu wejściach R i S wystąpi stan 0. W takim przypadku na obu wyjściach przerzutnika będzie stan 1. Ponieważ wyjścia Q i Q zgodnie z definicją przerzutnika powinny przyjmować wartości przeciwne, jest to tzw. stan niedozwolony.

Poniżej przedstawiamy model przerzutnika R-S zbudowanego z bramek NAND. Zwróć uwagę, iż po powrocie wejść do poziomu 1 przerzutnik zapamiętuje swój stan (stan wyjść się nie zmienia). Można go więc wykorzystać jako element pamiętający informację.

Przerzutnik R-S

Na schematach sieci logicznych pomija się zwykle strukturę wewnętrzną przerzutników. Zamiast tworzących je bramek rysujemy odpowiedni prostokąt z zaznaczonymi wejściami i wyjściami. Jeśli wejście jest aktywne przy stanie 0 (jak w tym przypadku), to rysujemy przy nim kółeczko (jak na wyjściu bramek NOT, NAND, NOR oraz EX-NOR).

Symbol logiczny przerzutnika RS wykonanego z bramek NAND

| S | R | Qn |

| 0 | 0 | Qn-1 |

| 1 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 1 | 0 |

Jeśli zamiast bramek NAND zastosujemy bramki NOR, to również powstanie przerzutnik R-S, lecz tym razem stanem aktywnym będzie wartość 1. Wyjścia przerzutnika zamieniają się miejscami (Q jest po przeciwnej stronie wejścia S na schemacie bramkowym). Jeśli na obu wejściach panuje stan 0, to przerzutnik pamięta poprzedni stan wyjścia, który w tabelce oznaczyliśmy jako Qn-1. Jest to sytuacja analogiczna do przerzutnika R-S zbudowanego z bramek NAND. Podanie na wejście S (Set - ustaw) stanu 1 spowoduje ustawienie wyjścia Q na 1. Podanie stanu 1 na wejście R (Reset - zeruj) spowoduje wyzerowanie wyjścia Q. Jeśli na obu wejściach S i R pojawi się stan 1, to wyjścia ustawią się w stan 0 i przestaną być komplementarne. Jest to więc stan niedozwolony.

Poniżej przedstawiamy model przerzutnika R-S oraz jego symbol logiczny.

Przerzutnik R-S

Symbol logiczny przerzutnika R-S wykonanego z bramek NOR

Zwykły przerzutnik R-S zmienia swój stan po zmianie stanów wejść S i R. Często jednak pożądane jest, aby zmiana taka następowała synchronicznie z sygnałem zegarowym, czyli taktem. W ten sposób możemy w sieci logicznej uniknąć wielu zakłóceń i hazardów oraz synchronizować poszczególne jej elementy. Wejście zegarowe możemy wyobrazić sobie jako swoisty zamek. Jeśli panuje na tym wejściu stan nieaktywny, to przerzutnik jest zamknięty i zmiana stanu wejść sterujących nic nie powoduje. Dopiero po pojawieniu się stanu aktywnego na wejściu zegarowym, przerzutnik odblokowuje wejścia sterujące i zmienia się zgodnie z tablicą przejść. Zwróć uwagę, iż nie powiedzieliśmy jaką wartość przyjmuje stan aktywny - może to być stan statyczny 0 lub 1 albo stan dynamiczny w momencie zmiany poziomu logicznego z 0 na 1 lub z 1 na 0 (tzw. zbocze narastające i opadające) w zależności od wykonania przerzutnika. Wejście taktujące oznaczamy zwykle literką C (ang Clock - zegar) lub T.

| C | S | R | Qn |

| 0 | 0 | 0 | Qn-1 |

| 0 | 0 | 1 | Qn-1 |

| 0 | 1 | 0 | Qn-1 |

| 0 | 1 | 1 | Qn-1 |

| 1 | 0 | 0 | Qn-1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Synchroniczny przerzutnik R-S otrzymujemy ze zwykłego przerzutnika R-S dodając dwie bramki NAND, których zadaniem jest separacja sygnałów S i R w czasie, gdy na wejściu taktującym C panuje stan nieaktywny (tutaj stan 0). Poniżej przedstawiamy schemat logiczny takiego przerzutnika oraz tabelkę jego stanów.

Przerzutnik synchroniczny R-S

W zależności od sposobu wyzwalania (odblokowywania wejść) przez sygnał zegarowy wyróżniamy cztery rodzaje przerzutników synchronicznych. Dla każdego z tych przypadków istnieje odpowiedni symbol wejścia zegarowego C.

|

Wyzwalanie wysokim poziomem sygnału zegarowego. Wejścia zostają odblokowane, gdy sygnał zegarowy C ma stan wysoki 1. Jeśli w tym stanie nastąpi zmiana sygnałów na wejściach przerzutnika, to również zmieni się jego stan na wyjściu. Opisany powyżej synchroniczny przerzutnik R-S ma takie własności. |

|

Wyzwalanie niskim poziomem sygnału zegarowego. Wejścia zostaną odblokowane, gdy sygnał zegarowy C przyjmie stan niski 0. Podobnie jak poprzednio zmiany na wejściach w trakcie trwania tego sygnału spowodują zmiany stanów wyjściowych przerzutnika. Taki typ taktowania oznaczamy kółeczkiem na wejściu zegarowym, podobnie jak wyjścia bramek odwracających NOT, NAND, NOR itp. Aby otrzymać taki przerzutnik z synchronicznego przerzutnika R-S, należy na jego wejściu C dodać inwerter. |

|

Wyzwalanie narastającym zboczem sygnału zegarowego. Wejścia są odczytywane przez przerzutnik tylko w bardzo krótkiej chwili, gdy sygnał zegarowy C mienia się ze stanu 0 na 1. Gdy sygnał zegarowy ustabilizuje się na poziomie 1, wejścia zostaną znów zablokowane i zmiany ich stanu nie wpłyną na stan sygnałów wyjściowych przerzutnika. Taki sposób wyzwalania umożliwia tworzenie przy pomocy przerzutników układów zliczających impulsy. Taki sposób wyzwalania jest odporny na zakłócenia. Wyzwalanie zboczem narastającym zaznaczane jest małym trójkątem rysowanym przy wejściu zegarowym. |

|

Wyzwalanie opadającym zboczem sygnału zegarowego. Wejścia przerzutnika są odczytywane w momencie zmiany stanu sygnału zegarowego z poziomu 1 na 0. Gdy sygnał zegarowy ustabilizuje się na poziomie 0, wejścia są blokowane, aż do następnego zbocza opadającego. Wyzwalanie zboczem opadającym zaznaczane jest małym trójkątem i kółkiem przy wejściu zegarowym. |

Przerzutnik wyzwalany poziomem sygnału zegarowego nosi nazwę przerzutnika statycznego lub zatrzasku (ang. latch - klamka, zatrzask). Przerzutniki wyzwalane zboczem nazywamy przerzutnikami dynamicznymi.

| C | D | Qn |

| 0 | 0 | Qn-1 |

| 0 | 1 | Qn-1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Przerzutnik typu D powstaje w prosty sposób z synchronicznego przerzutnika R-S przez dodanie jednego invertera na wejściu R. Przerzutnik ten ma ogromne zastosowanie w tworzeniu różnych rejestrów oraz liczników. Działanie przerzutnika polega na przenoszeniu stanu z wejścia D na wyjście Q w czasie trwania stanu aktywnego na wejściu C. Gdy wejście wyzwalające przejdzie w stan nieaktywny, przerzutnik zapamiętuje ostatnio ustawiony stan.

Przerzutnik typu D

Symbol logiczny przerzutnika D

Przerzutniki D produkowane są w kilku wersjach różniących się sposobem wyzwalania:

| J | K | Qn |

| 0 | 0 | Qn-1 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Qn-1 |

Ostatnim, opisywanym przez nas przerzutnikiem jest bardzo popularny przerzutnik J-K. Literki J i K zostały wybrane arbitralnie i nie odnoszą się do funkcji spełnianych przez wejścia. Przerzutnik ten powstaje z synchronicznego przerzutnika R-S wyzwalanego zboczem opadającym po dodaniu dwóch bramek AND. W przeciwieństwie do przerzutnika R-S tutaj wszystkie stany wejść są dozwolone i wywołują dobrze zdefiniowaną zmianę stanów wyjść, co obrazuje tabelka. Wejście J można traktować jako wejście ustawiające, a K jako zerujące. Jeśli na obu wejściach J i K pojawi się stan 1, to przy opadającym zboczu sygnału zegarowego wyjście Q przyjmie stan przeciwny (zmieni się z 1 na 0 lub z 0 na 1). W tabelce nie zaznaczono sygnału zegarowego, gdyż nie jest to potrzebne.

Synchroniczny przerzutnik J-K

Teraz pokażemy kilka przykładowych zastosowań poznanych elementów logicznych w układach powszechnie spotykanych w technice cyfrowej. Przy tworzeniu naszych układów cyfrowych mamy do dyspozycji następujące cegiełki:

Rejestr jest układem cyfrowym, który zapamiętuje informację w postaci słowa

binarnego o określonej długości (liczbie bitów).

Rejestr powinien umożliwiać zapis informacji, odczyt zapamiętanej informacji

oraz zerowanie. Najczęściej rejestry konstruowane są z przerzutników

D lub

J-K. Poniżej przedstawiamy przykładowy schemat logiczny

rejestru 4 bitowego z możliwością zapisu, odczytu i zerowania. Rejestr został

zaprojektowany z przerzutników

D typu SN74LS74. W każdym

układzie znajdują się dwa przerzutniki D,

potrzebne są więc dwa takie układy scalone.

Rejestr 4-bitowy

Rejestr posiada cztery wejścia danych (D1, D2, D3, D4), cztery wyjścia danych (Q1, Q2, Q3, Q4), wejście zapisu (ZAPIS) oraz wejście zerowania (ZR). Działanie rejestru jest bardzo proste. Informację przechowywaną w rejestrze można w każdej chwili odczytać z wyjść Qn. Wejścia Dn służą do wprowadzania informacji do rejestru. Zapis następuje przy narastającym zboczu sygnału ZAPIS (zmiana z 0 na 1). Podanie wysokiego stanu na wejście ZR spowoduje wyzerowanie wszystkich przerzutników.

Zwróć uwagę na następujące rzeczy:

Rejestry pozwalają przechowywać pojedyncze słowa binarne. W systemach komputerowych bardzo często występuje potrzeba zapamiętywania większej ilości informacji. Do tego celu opracowano specjalne urządzenie, zwane pamięcią. Pamięć możemy potraktować jako zbiór rejestrów, które w tym przypadku nazywać będziemy komórkami. Każda komórka pozwala zapamiętywać określoną liczbę bitów (zależy to od liczby zastosowanych przerzutników pamięciowych), najczęściej jest to 8, 16 lub 32 bity. Aby umożliwić łatwy dostęp do poszczególnych komórek, każda z nich ma przydzielony kolejny numer, zwany adresem. Adres określa położenie komórki w obszarze pamięci.

Z rozważań tych wynika, iż pamięć powinna posiadać kilka rodzajów wejść i wyjść:

Aby zrozumieć działanie pamięci, zaprojektujemy przykładową pamięć o

pojemności 4 bitów. Każda komórka tej pamięci będzie przechowywała dokładnie 1

bit informacji. Adresy komórek będą kolejnymi liczbami 0,1,2 i 3. Pamięć będzie

posiadać jedno wejście danych D, jedno wyjście danych Q, dwa wejścia adresowe A0

i A1, na które będziemy podawać adresy komórek w postaci binarnej,

jedno wejście sterujące zapisem informacji w komórce - z uwagi na separacje

wejścia i wyjścia danych nie jest konieczne osobne wejście sterujące odczytem,

podanie adresu na wejścia adresowe powoduje automatyczne umieszczenie na wyjściu

Q zawartości wybranej komórki pamięci.

| adres | komórka | ||||

| A1 | A0 | C0 | C1 | C2 | C3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

Najpierw musimy zaprojektować układ wybierający komórki na podstawie adresu. Układ taki nazywa się dekoderem adresowym. Posiada on tyle wejść, z ilu bitów składa się adres komórki (u nas 2) oraz tyle wyjść, ile występuje w pamięci komórek (u nas 4). Dekoder ten powinien działać według podanej obok tabelki. Na kolejnych wyjściach C0 ... C3 powinien pojawiać się stan 1. Numer wyjścia zależy od podanego na wejścia A1 i A0 adresu w formie liczby dwójkowej. Na pozostałych wyjściach dekodera panuje wtedy stan 0. Dzięki temu układowi będziemy mogli wybierać odpowiednie komórki w naszej pamięci. Wypiszmy funkcje logiczne poszczególnych wyjść Cn:

| C0 = A1

·

A0 C1 = A1 · A0 C2 = A1 · A0 C3 = A1 · A0 |

Do zrealizowania takiego dekodera potrzebne nam będą dwa inwertery oraz cztery bramki AND:

Dekoder adresowy

Następnym niezbędnym elementem pamięci będzie układ odczytu komórki. Do wejść

tego układu doprowadzamy sygnały Cn

z dekodera adresowego oraz z wyjść Qn

poszczególnych przerzutników. Na wyjściu pojawia się stan wyjściowy tego

przerzutnika, dla którego sygnał Cn

z dekodera adresowego ma poziom 1. Zrealizujemy go za pomocą czterech bramek

AND oraz czterowejściowej bramki OR.

Układ odczytu komórek pamięci

Trzecim niezbędnym elementem są komórki wraz z układem zapisu. Układ ten korzysta z wyjść Cn dekodera adresu oraz z sygnału ZAPISZ, nad którymi dokonuje operacji AND i wynik przekazuje do wejść taktujących przerzutników. W ten sposób dane zostaną zapisane tylko w jednej komórce. Wszystkie wejścia danych są połączone ze sobą.

Komórki pamięci wraz z układem zapisu

Pozostało nam jedynie połączyć ze sobą wszystkie trzy składniki. W ten sposób otrzymujemy kompletny moduł pamięci 4 bitowej.

Pamięć o pojemności 4 bitów

Oczywiście zastosowanie praktyczne takiej pamięci jest wątpliwe. Zaprojektowaliśmy ją tylko w celach edukacyjnych. Pamięć tę można łączyć równolegle z takimi samymi modułami, uzyskując w ten sposób komórki o większej liczbie bitów (wejścia pamięci mogą znacznie obciążać układy współpracujące i przy większej pojemności należałoby tutaj wprowadzić bramki buforujące).. Jeśli dokładnie prześledziłeś ten projekt, to powinieneś zrozumieć sposób działania większych pamięci. Nie różnią się one zbytnio koncepcją od przedstawionego tutaj modelu. Posiadają nawet te same bloki logiczne, odpowiednio rozbudowane.

Z punktu widzenia użytkownika pamięć działa następująco:

Licznik jest układem zliczającym w pewnym kodzie binarnym

(najczęściej NBC) impulsy podawane na wejście

zliczające. Liczniki konstruowane są z odpowiednio skonfigurowanych

przerzutników

synchronicznych typu D lub

J-K. Podstawowym elementem jest tzw. dzielnik lub dwójka

licząca. Jest to przerzutnik, który przy każdym impulsie zegarowym zmienia swój

stan na przeciwny. Poniżej przedstawiam model takiej dwójki liczącej utworzony z

dynamicznego przerzutnika D

wyzwalanego narastającym zboczem sygnału zegarowego.

Dwójka licząca

Ponieważ do wejścia D podłączone jest wyjście komplementarne Q przerzutnika, to przy każdym impulsie zegarowym stan wyjścia Q zmienia się na przeciwny. Licznik uzyskamy łącząc w szereg odpowiednią liczbę dwójek liczących. Poniżej przedstawiamy model licznika 4-bitowego.

Cztero bitowy licznik asynchroniczny

Licznik tego typu nosi nazwę licznika asynchronicznego, ponieważ poszczególne przerzutniki nie przełączają się jednocześnie, lecz z pewnym opóźnieniem wynikającym z czasu propagacji sygnału w poprzednim przerzutniku (wyjście Q steruje wejściem zegarowym C następnego przerzutnika, więc zmiana stanu nastąpi dopiero przy przejściu tego wyjścia ze stanu 0 na 1). Ogranicza to maksymalną częstotliwość zliczania impulsów. Na wejście C podajemy impulsy do zliczania. Na wyjściach Q3, Q2, Q1 oraz Q0 otrzymujemy wartość dwójkową, która jest numerem kolejnego, zliczonego impulsu zegarowego. Poniżej przedstawiamy wykres czasowy stanów poszczególnych wyjść licznika. Wykresy takie często stosuje się przy projektowaniu urządzeń cyfrowych.

Wykres stanów na poszczególnych wyjściach licznika

Licznik zlicza od wartości 0 (wszystkie wyjścia Q mają stan 0) do 15 (wszystkie wyjścia Q mają stan 1). Gdy osiągnie on stan 15 i nadejdzie kolejny impuls zegarowy, licznik przewinie się na 0 i zliczanie nastąpi od nowa. Mówimy, iż licznik zlicza z modułem 16. Konstruowanie liczników asynchronicznych zliczających z innym modułem polega na zerowaniu wszystkich przerzutników, gdy stan licznika osiągnie wartość tego modułu. Do realizacji tego zadania wykorzystywana jest najczęściej bramka NAND. Poniżej przedstawiamy licznik zbudowany z trzech przerzutników D, zliczający z modułem 6 (tzn. na jego wyjściu będą pojawiały się stany kolejno 0, 1, 2, 3, 4, i 5 - stan 6 również pojawi się, ale na bardzo krótki okres czasu równy czasowi propagacji bramki NAND oraz przerzutników, po czym wszystkie przerzutniki zostaną wyzerowane).

Licznik o module 6

Działanie tego licznika jest dosyć proste. Zliczane są kolejne impulsy zegarowe, co powoduje odpowiednią zmianę stanu wyjść Q0, Q1, Q2. Gdy na wyjściach Q1 i Q2 pojawi się stan 1, co odpowiada wartości binarnej 6 (Q2 = 1, Q1 = 1, Q0 = 0) zadziała bramka NAND i na jej wyjściu pojawi się stan 0. Ponieważ wyjście tej bramki połączone jest z wejściami zerowania przerzutników, to licznik zostanie wyzerowany - na wszystkich jego wyjściach Q pojawi się stan 0, a bramka NAND wróci do stanu 1. Nadejście kolejnego impulsu zegarowego na wejściu C rozpocznie nowy cykl zliczania. Poniżej przedstawiamy wykres czasowy tego licznika. Moment zadziałania bramki NAND zaznaczyliśmy kolorem czerwonym.

Wykres stanów logicznych na wejściu C oraz na wyjściach Q licznika

Z wykresu czasowego wynika, iż w tak skonstruowanym liczniku na wyjściach przez krótką chwilę utrzymuje się stan 6. Może to mieć niepożądane skutki dla układów logicznych, którymi licznik steruje. W takich sytuacjach stosujemy inne liczniki, zwane synchronicznymi. W liczniku synchronicznym stany wszystkich przerzutników zmieniają się równocześnie - sygnał zegarowy jest doprowadzony do wejścia każdego z przerzutników. Przełączaniem przerzutników steruje odpowiednio skonstruowana sieć logiczna. Zaprojektowanie takiego licznika może być trochę skomplikowane. lecz nie przekracza możliwości uważnego czytelnika. Dla przykładu przedstawię wam sposób postępowania przy tworzeniu synchronicznego licznika o module 6.

Najpierw musimy utworzyć tabelkę kolejnych stanów wyjść licznika. które będą zmieniane kolejno przy każdym zboczu narastającym sygnału zegarowego. Tabelka jest następująca:

| n | Q2 | Q1 | Q0 |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 |

| 4 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 |

| 6 | 0 | 0 | 0 |

Z tabelki tej można wyciągnąć informację o tym, jaki stan powinien wystąpić na wejściu D każdego przerzutnika przed impulsem zegarowym, aby na wyjściach otrzymać stan następny. Na przykład, jeśli wyjścia licznika są w stanie 3 (Q2 = 0, Q1 = 1, Q0 = 1), to następnym stanem po nadejściu impulsu zegarowego będzie stan 4, czyli Q2 = 1, Q1 = 0, Q0 = 0. Aby tak się stało, przy stanie 3 na wejściach przerzutników muszą wystąpić stany D2 = 1, D1 = 0, D0 = 0, co wynika bezpośrednio z własności przerzutnika typu D. Możemy więc utworzyć tabelkę stanów wejść D w funkcji wyjść Q:

| n | Q2 | Q1 | Q0 | D2 | D1 | D0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 | 0 |

| 4 | 1 | 0 | 0 | 1 | 0 | 1 |

| 5 | 1 | 0 | 1 | 0 | 0 | 0 |

| 6 | 0 | 0 | 0 |

Od impulsu 6 cykl się powtarza. Stany wejść D są funkcjami logicznymi stanów

wyjść Q, co możemy zapisać następująco:

D2 = d2(Q2, Q1.

Q0)

D1 = d1(Q2, Q1. Q0)

D0 = d0(Q2, Q1. Q0)

Zadanie sprowadza się zatem do znalezienia postaci tych funkcji. Zrobimy to przy pomocy odpowiednich map Karnaugha utworzonych zgodnie z powyższą tabelką. Pozycji oznaczonej na czerwono (stan 111 wyjść) licznik nigdy nie osiąga, więc można tam wpisać dowolną wartość. Skorzystałem z tego faktu, aby uprościć maksymalnie funkcje przełączania przerzutników.

| D0 | Q1Q0 | D0 = Q0 | ||||

| 00 | 01 | 11 | 10 | |||

| Q2 | 0 | 1 | 0 | 0 | 1 | |

| 1 | 1 | 0 | 0 | 1 | ||

| D1 | Q1Q0 |

D1 = Q2·Q1·Q0+Q1·Q0 |

||||

| 00 | 01 | 11 | 10 | |||

| Q2 | 0 | 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 0 | 1 | ||

| D2 | Q1Q0 |

D2 = Q1·Q0+Q2·Q0 |

||||

| 00 | 01 | 11 | 10 | |||

| Q2 | 0 | 0 | 0 | 1 | 0 | |

| 1 | 1 | 0 | 1 | 1 | ||

Poniżej przedstawiamy model tego licznika. Możesz klikać myszką w zaznaczone na niebiesko pole wejścia zegarowego - spowoduje to zmianę stanu licznika na stan następny. Obserwuj wejścia D i wyjścia Q.

Model synchronicznego licznika z modułem 6

Licznik ten nie posiada wady liczników asynchronicznych polegającej na pojawianiu się stanu 6 na wyjściach. Przeniesienia są generowane jednocześnie na podstawie aktualnego stanu licznika, więc może on działać z dużo większą częstotliwością. Zwróć uwagę, iż w podany sposób możemy zaprojektować dowolny układ sekwencyjny, który wraz z kolejnymi impulsami zegarowymi przyjmuje wybrane stany wyjść.

Komputer w trakcie pracy musi utrzymywać kontakt z otoczeniem. Jednym ze sposobów jest wyświetlanie informacji. W pierwszych latach rozwoju komputerów jako wskaźniki świetlne stosowano zwykłe żarówki. Jednak żarówki, pomimo dużych zalet, mają również poważne wady. Światło powstaje w nich na skutek rozgrzania do wysokiej temperatury przepływającym prądem elektrycznym cienkiego włókienka wykonanego z przewodnika trudno topliwego (najczęściej jest to wolfram, który topi się dopiero w temperaturze 3407°C). Domyślasz się zapewne, iż nie jest to specjalnie wydajny proces - tylko mały procent dostarczonej energii zamieniany jest w światło użyteczne. Reszta idzie na promieniowanie cieplne, które nagrzewa żarówkę, a poprzez nią otoczenie. Włókienko wolframowe musi być umieszczone w próżni, aby nie następowało jego utlenianie pod wpływem wysokiej temperatury. Trwałość żarówki również nie jest najlepsza.

|

| LED = Light

Emitting Diode Dioda Emitująca Światło |

Z rozwiązaniem tych problemów przyszła nowa gałąź działalności człowieka w XX w. - elektronika. Dobierając odpowiednie materiały półprzewodnikowe można wytworzyć specjalny element, nazwany LED - Light Emitting Diode - Dioda Emitująca Światło, zwana również diodą elektroluminescencyjną. LED zachowuje się jak zwykła dioda, tzn. przepuszcza prąd tylko w jednym kierunku. W czasie przepływu prądu wytwarzane jest światło monochromatyczne (tzn. czerwone, żółte, zielone, niebieskie itp.). W przeciwieństwie do żarówki światło nie powstaje na skutek wysokiej temperatury - można się o tym w prosty sposób przekonać dotykając świecącej diody LED (masz je w swoim komputerze PC) - jest zimna. Fotony powstają w procesach fizycznych odbywających się w strukturze półprzewodnika. Procesy te są bardzo wydajne, dlatego diody LED pobierają niewiele energii elektrycznej. Z diod LED budowane są różnego rodzaju wskaźniki świecące - od prostych, pojedynczych LED-ów do całych ich zespołów.

Diody LED można podłączać do wyjść układów logicznych na dwa sposoby. W pierwszym dioda będzie świecić, gdy na wyjściu układu panuje stan wysoki, a w drugim gdy niski.

W obu przypadkach w szereg z diodą LED należy włączyć opornik R, który ograniczy prąd świecenia diody do 20 mA. Wartość tego opornika obliczamy wg przybliżonego wzoru:

| R = (4,5 - ULED) / 0,02 |

Parametr ULED określa wartość napięcia przewodzenia diody LED. Można odczytać go z katalogu producenta lub przyjąć w przybliżeniu 1,5 V dla diod LED czerwonych, 2,5 V dla zielonych i żółtych. Wynika stąd, iż dla diod czerwonych zastosujemy opornik R=150 Ohm, a dla zielonych i żółtych R=100 Ohm.

Diody LED mogą być łączone w większe zespoły w celu wyświetlania znaków, np. cyfr lub liter. Bardzo dużą popularnością cieszą się tzw. wskaźniki 7-segmentowe LED. Składają się one z 7 diod LED (czasami jest ich 8, gdy występuje przecinek) połączonych katodami lub anodami. Sterując świeceniem odpowiednich diod LED można wyświetlać cyfry oraz niektóre literki. Poniżej przedstawiamy model takiego wskaźnika. Możesz zapalać i gasić poszczególne segmenty klikając w nie myszką.

|

|

||

|

|

|

|

|

|

||

|

|

|

|

|

|

||

Innym rodzajem wyświetlacza z diod LED jest wyświetlacz alfanumeryczny, który potrafi przedstawić wszystkie litery alfabetu oraz znaki interpunkcyjne. Buduje się go najczęściej z diod LED ułożonych w formie matrycy 5 kolumn na 7 wierszy, co daje w sumie 35 punktów świetlnych. Zapalając odpowiednie diody na takim wyświetlaczu można uzyskać dosyć wyraźne znaki. Wyświetlacze matrycowe pracują w grupach tworzących wiersze (po 16, 20, 24,32 i więcej wyświetlaczy w wierszu). Do sterowania takimi wyświetlaczami konstruuje się specjalne układy zwane sterownikami. Zawierają one sprzętowy dekoder kodu ASCII na kod wyświetlacza, w tym wypadku każdy kod 8 bitowy ASCII jest przetwarzany na słowo 35 bitowe, które steruje świeceniem poszczególnych diod na wyświetlaczu. Zadaniem komputera jest przekazywanie poszczególnych kodów literek. Sterownik wyświetlacza przetwarza je następnie na odpowiednie kody wewnętrzne. Oprócz zwykłych literek sterowniki przyjmują również znaki specjalne, które będziemy nazywać kodami sterującymi. Kod sterujący wywołuje wykonanie określonej operacji na wyświetlaczu, np. usunięcie wszystkich literek z wiersza, skasowanie znaku, przesunięcie znaków całego wiersza, itp.

|

| Matryca LED |

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2026 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.