w I-LO w Tarnowie

Materiały dla uczniów liceum

Wyjście Spis treści Wstecz Dalej

Autor artykułu: mgr Jerzy Wałaszek

Konsultacje: Wojciech Grodowski, mgr inż. Janusz Wałaszek

©2024 mgr Jerzy Wałaszek

I LO w Tarnowie

|

Serwis Edukacyjny w I-LO w Tarnowie

Materiały dla uczniów liceum |

Wyjście Spis treści Wstecz Dalej

Autor artykułu: mgr Jerzy Wałaszek |

©2024 mgr Jerzy Wałaszek

|

Nazwa przerzutnik wzięła się stąd, iż sygnały wejściowe mogą "przerzucić" pamiętany w przerzutniku stan wewnętrzny na przeciwny.

Pierwszy elektroniczny przerzutnik typu flip–flop wynaleziony został w roku 1919 przez dwóch naukowców – Williama Ecclesa i F.W. Jordana. Początkowo nazywano go układem przełączającym Ecclesa–Jordana (ang. Eccles-Jordan trigger). Układ ten zbudowany był z dwóch aktywnych elementów elektronicznych – lamp elektronowych (pierwsze tranzystory wynaleziono dopiero w roku 1949). Angielska nazwa flip flop powstała później jako efekt naśladowania dźwięku wydawanego przez głośniki podłączone do wzmacniacza akustycznego sterowanego przez wymieniony przerzutnik.

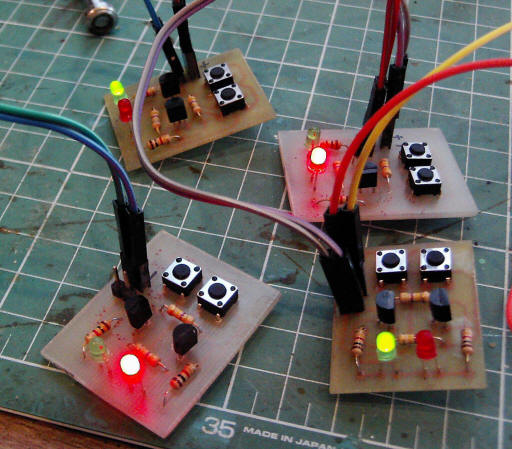

Na kursie Eagle projektowaliśmy prosty przerzutnik z tranzystorów:

Przerzutnik ten działa w sposób następujący:

Z dwóch tranzystorów zawsze jeden będzie przewodził, a drugi będzie zablokowany. Załóżmy, że przewodzi tranzystor T1 i świeci dioda czerwona LED1. Napięcie bazy T2 pobierane jest z kolektora T1. Ponieważ T1 przewodzi, to na jego kolektorze panuje niskie napięcie. Zatem baza T2 jest sterowana niskim napięciem, poniżej 0,65V. Powoduje to, że stan zablokowania T2 się utrzymuje. Baza T1 pobiera napięcie z kolektora T2. Skoro T2 jest zablokowany, to na jego kolektorze występuje wyższe napięcie, które powoduje wysterowanie bazy T1 i podtrzymanie przewodzenia T1. Widać z tego wyraźnie, że stan ten jest stabilny i sam się podtrzymuje.Jeśli teraz naciśniesz przycisk W2, to zewrzesz bazę tranzystora T1 do masy. Tranzystor T1 zablokuje się i wzrośnie napięcie na jego kolektorze. To wyższe napięcie przeniesie się na bazę tranzystora T2 i odblokuje go. Dioda czerwona LED1 zgaśnie, a zaświeci się dioda zielona LED2. Gdy zwolnisz przycisk W2, to na baza tranzystora T1 będzie sterowana napięciem z kolektora tranzystora T2. Skoro tranzystor T2 przewodzi, to na jego kolektorze jest niskie napięcie. W efekcie tranzystor T1 pozostanie zablokowany, a tranzystor T2 będzie odblokowany. Przerzutnik przełączył się w drugi stabilny stan. Naciśnięcie przycisku W1 z powrotem przywróci stan pierwotny.

Wygląda to niepozornie, ale tak właśnie działa przerzutnik: przełącza się pod wpływem sygnałów wejściowych i pamięta ten stan, dopóki inne sygnały wejściowe mu tego stanu nie zmienią.

| Przerzutnik S-R z bramek NAND | Przerzutnik S-R z bramek NOR | |||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

Przerzutnik S-R posiada dwa wejścia oznaczone:

|

S (ang. Set) – wejście

ustawiające R (ang. Reset) – wejście zerujące |

oraz dwa wyjścia Q i Q. Na wyjściach tych pojawia się stan logiczny pamiętany w przerzutniku. Wyjście Q jest negacją wyjścia Q.

Dla przerzutnika z bramek NAND podanie stanu niskiego 0 na wejście S spowoduje ustawienie stanu 1 na wyjściu Q (na Q będzie negacja, czyli stan 0). Podanie stanu 0 na wejście R powoduje wyzerowanie przerzutnika, czyli ustawienie na wyjściu Q stanu 0. Gdy oba wejścia znajdą się w stanie wysokim 1, to przerzutnik utrzymuje swój poprzedni stan, co w tabelce funkcji oznaczamy jako Qn-1. Są to tzw. stany nieaktywne wejść. Jeśli oba wejścia przyjmą jednocześnie stan 0, to oba wyjścia przejdą w stan wysoki, lecz powrót wejść do stanu nieaktywnego spowoduje niezdefiniowane zachowanie się przerzutnika (zależne od czasu propagacji bramek). Dlatego taki stan nazywa się stanem zabronionym i oznaczyliśmy go kolorem czerwonym. Należy go unikać

Przerzutnik z bramek NOR działa podobnie, tylko stanami aktywnymi są stany wysokie 1. Pobaw się apletami, które umieściliśmy powyżej. Kolor czerwony oznacza stan wysoki , niebieski stan niski 0.

Działanie przerzutnika NAND oparte jest na sprzężeniu wyjść z wejściami. W ten sposób przerzutnik przełączony w określony stan utrzymuje go, gdy sygnały wejściowe są nieaktywne. Przeanalizujmy przerzutnik S-R z bramek NAND. Załóżmy, że na obu wejściach są stany wysokie 1, a na wyjściu Q jest stan 1. Sytuacja jest taka, jak na poniższym rysunku:

Ponieważ jedno z wejść bramki B2 jest połączone z wyjściem bramki B1 (sprzężenie zwrotne, czyli połączenie wejścia z wyjściem układu), to na obu wejściach bramki B1panują wysokie stany logiczne 1. Zgodnie z funkcją NAND realizowana przez bramkę B2 na jej wyjściu panuje wtedy stan 0. Z kolei jedno z wejść bramki B1 jest połączone z wyjściem bramki B2, zatem trafia tam stan 0 i stany obu wejść są różne. To da stan 1 na wyjściu bramki B1 i stan w przerzutniku jest podtrzymywany samoczynnie. Przerzutnik pamięta ten stan:

Z uwagi na symetrię układu w sytuacji odwrotnej jest analogicznie. Jeśli na wyjściu Q panuje stan 0, to będzie on podtrzymywany przy stanach niskich na obu wejściach sterujących przerzutnika:

Teraz załóżmy, że wejście S przyjmuje stan niski 0, a wejście R pozostaje w stanie wysokim 1.

Bez względu na poprzedni stan przerzutnika na wyjściu bramki B1 zostanie wymuszony stan 1:

Gdy wejście S powróci do stanu nieaktywnego 1, to nowy stan przerzutnika zostanie podtrzymany,, jak pokazaliśmy wyżej. Zatem stan niski na wejściu S ustawia przerzutnik w stan 1, stąd nazwa angielska Set, czyli ustaw. Zwróć uwagę, że po ustawieniu stanu 1 na wyjściu Q, drugie wyjście Q przyjmuje stan przeciwny 0.

Ponieważ układ jest symetryczny, to podanie stanu 0 na wejście R spowoduje ustawienie wyjścia Q na 1, a Q na 0:

Tutaj również po powrocie wejścia R do stanu nieaktywnego 1 przerzutnik utrzyma nowy stan. Stan niski na wejściu R zeruje przerzutnik, dlatego przyjęto dla niego nazwę angielską Reset, czyli zeruj.

Przeanalizuj dokładnie powyższe rysunki i wyjaśnienia aż zrozumiesz zasadę działania przerzutnika S-R. Spróbuj w podobny sposób przeanalizować pracę przerzutnika z bramek NOR.

Przerzutniki S-R często są stosowane do odczytu stanu przełączników mechanicznych. Przełączniki te mają taką własność, iż w momencie przełączenia styki często wykonują drgania sprężyste, co powoduje powstawanie serii krótkich impulsów napięciowych, które mogą być szkodliwe dla układów cyfrowych (taka seria będzie interpretowana jako kilka wciśnięć przycisku):

Rozwiązaniem jest zastosowanie przerzutnika S-R z bramek NAND.

Drgania styków nie przeniosą się na wyjście, ponieważ sygnał wejściowy S lub R ustawi odpowiednio stan Y i ewentualne zmiany tego sygnału nie spowodują już zmiany poziomu logicznego wyjścia Y. Oporniki wymuszają stan wysoki na wejściach przerzutnika.

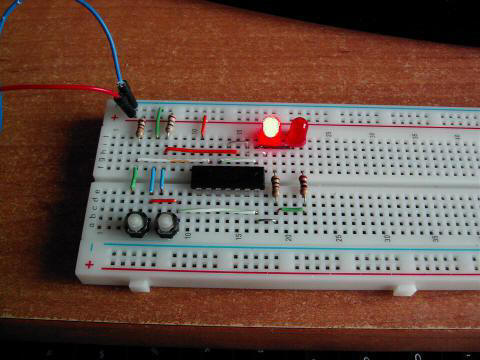

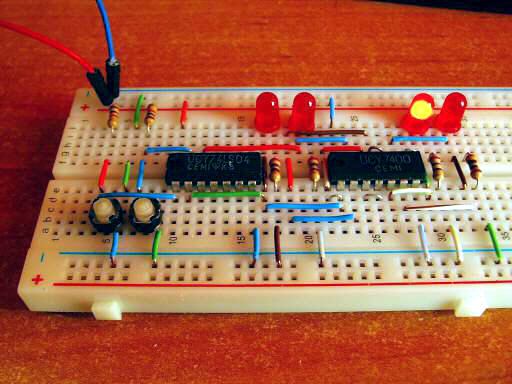

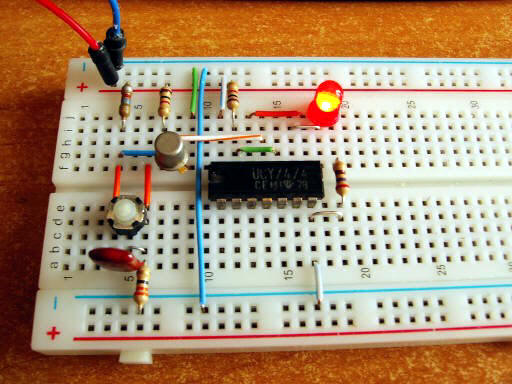

Zbudujemy poniższy układ cyfrowy z przerzutnikiem S-R na dwóch bramkach NAND z układu SN7400.

SN7400: 4 x 2NAND

|

Spis elementów:

|

|

|

Gdy nie jest naciśnięty żaden z dwóch przycisków, to na wejściach obu bramek pojawia się stan logiczny 1, ponieważ są one podłączone do +5V poprzez oporniki 1kΩ. Przy takich sygnałach sterujących przerzutnik utrzymuje (pamięta) ostatni swój stan. Jeśli teraz naciśniemy przycisk S, to wejście górnej bramki zostanie zwarte do masy, a zatem otrzyma stan logiczny 0. Spowoduje to wymuszenie stanu 1 na wyjściu tej bramki i zapali się dioda Q. Wyjście górnej bramki jest połączone z wejściem bramki dolnej. Zatem na obu wejściach dolnej bramki pojawi się stan logiczny 1. Bramka dolna ustawi na swoim wyjściu stan 0 i dioda Q zgaśnie (jeśli wcześniej była zapalona). Ponieważ układ jest symetryczny, to przy naciśnięciu przycisku R na wyjściu dolnej bramki pojawi się stan 1 i wymusi on stan 0 na wyjściu bramki górnej. A zatem przerzutnik przejdzie w stan "odwrotny". Jeśli naciśniesz oba przyciski naraz, to na obu wyjściach przerzutnika pojawi się stan logiczny 1 i obie diody zapalą się. Jest to stan zabroniony (nie w sensie jakiegoś zakazu, lecz w tym stanie wyjścia Q i Q nie są w stanach przeciwnych).

Przy opisie sieci logicznych wspomnieliśmy o zjawisku hazardu, czyli nieokreślonych stanach w sieciach logicznych spowodowanymi różnymi czasami propagacji bramek. Sieć logiczna ustala się, gdy sygnał o najdłuższym czasie propagacji przejdzie z wejścia na wyjście. Sposobem radzenia sobie z hazardami jest wprowadzenie synchronizacji w postaci impulsów zegarowych, które są generowane z odpowiednio dobranymi przerwami. Czas pomiędzy impulsami zegarowymi sieć wykorzystuje na ustalenie swojego stanu logicznego, czyli na wygaśnięcie hazardów.

Przerzutnik S-R można łatwo tak zaprojektować, aby mógł zmieniać swój stan tylko w okresie, gdy sygnał zegarowy ma stan wysoki 1. Dzięki temu eliminujemy przypadkowe zmiany stanu przerzutnika spowodowane hazardami w sterującej nim sieci.

Wystarczy dodać na wejściu dwie bramki NAND dla przerzutnika S-R zbudowanego z bramek NAND lub dwie bramki AND dla przerzutnika zbudowanego z bramek NOR:

|

|

< |  |

|

Przerzutnik synchroniczny S-R posiada dodatkowe wejście C (ang. Clock, zegar). Jeśli na tym wejściu panuje stan logiczny 0, to bramki wejściowe wymuszają stany nieaktywne sygnałów sterujących przerzutnikiem i przerzutnik pamięta swój poprzedni stan bez względu na zmiany wejść S i R (X w tabelce oznacza dowolny stan logiczny). Gdy na wejście C zostanie podany wysoki poziom logiczny 1, to bramki wejściowe odblokowują sygnały sterujące i przerzutnik może zmieniać swój stan.

Na schematach ideowych przerzutniki zwykle przedstawia się w postaci prostokątów. Kółeczko na wejściu lub wyjściu oznacza negację sygnału lub aktywność przy niskim poziomie 0.

|

Przerzutnik S-R. Wejścia aktywne w stanie niskim |

|

|

Przerzutnik R-S typu Latch. Wejścia aktywne w stanie wysokim. |

|

|

Synchroniczny przerzutnik S-R. Wejścia aktywne w stanie wysokim przy wysokim stanie wejścia C. |

|

|

|

Wejście D jest wejściem informacyjnym. Wejście C to tzw. wejście taktujące, zegarowe (ang. C = Clock). Jeśli na tym wejściu panuje stan wysoki 1, to wyjście Q przyjmuje stan wejścia D. Gdy wejście C przejdzie w stan niski 0, to na wyjściu Q zostanie "zatrzaśnięty" stan wejścia D, który był przed tą zmianą. Z tego powodu tego typu przerzutnik nosi nazwę zatrzasku (ang. latch).

Sieć logiczna przerzutnika D typu latch składa się z dwóch bramek tworzących poznany wcześniej przerzutnik S-R oraz dodatkowych dwóch bramek sterujących. Jeśli na wejściu C panuje stan 0, to na wyjściu obu bramek sterujących pojawiają się stany wysokie 1, które podawane są na oba wejścia przerzutnika S-R. Ponieważ dla przerzutnika S-R z bramek NAND są to stany nieaktywne, pamięta on swój poprzedni stan. Jeśli teraz na wejściu C pojawi się stan wysoki, to stan wyjść bramek sterujących będzie zależał od stanu wejścia D. Dla D równego 0 na wyjściu górnej bramki sterującej będzie stan 1, a na wyjściu dolnej będzie stan 0. Spowoduje to przełączenie wyjścia Q na stan niski 0, czyli taki sam jak na wejściu D. Jeśli na wejściu D pojawi się stan 1, to wyjście górnej bramki sterującej przyjmie stan 0, a wyjście dolnej bramki stan 1. Spowoduje to przełączenie wyjścia Q w stan 1, czyli znów taki sam jak stan wejścia D.

Aby przetestować przerzutnik D latch, zbudujemy prostą sieć logiczną. Do 4 bramek NAND tworzących przerzutnik D latch dodamy dwa inwertery NOT, aby wygodnie sterować sygnałami wejściowymi – dzięki nim naciśnięcie przycisku będzie podawało stan 1 na wejścia przerzutnika D.

SN7400: 4 x 2NAND |

SN7404: 6 x NOT |

Spis

elementów:

|

|

|||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||

Zasada działania układu jest następująca:

Przerzutników D zwykle nie buduje się z pojedynczych bramek. W handlu spotkasz układy scalone, które zawierają gotowe przerzutniki D-latch:

Przerzutnik D Latch jest wyzwalany stanem wysokim na wejściu zegarowym C. Istnieją również rozwiązania przerzutników D, gdzie zapamiętanie stanu wejścia D następuje tylko w bardzo krótkim czasie, gdy sygnał zegarowy zmienia swój poziom, np. z 1 na 0 lub z 0 na 1. Mówimy wtedy o przerzutniku wyzwalanym zboczem sygnału zegarowego. Gdy sygnał zegarowy ma stały poziom, zmiany na wejściu D nie przenoszą się na wyjście Q.

Tego typu przerzutnik można zbudować z dwóch przerzutników D Latch pracujących w tzw. trybie Master–Slave (pan–sługa). Poniżej przedstawiona jest symulacja takiego przerzutnika.

|

|

|

Przeanalizujmy ten układ.

Zwróć uwagę na sposób oznaczenia wejścia zegarowego C. Nie jest on przypadkowy i informuje nas o sposobie wyzwalania zmiany stanu przerzutnika. Stosuje się następujące oznaczenia dla wejść:

|

wyzwalanie poziomem 1 |

|

wyzwalanie poziomem 0 |

|

wyzwalanie zboczem dodatnim: 0 → 1 |

|

wyzwalanie zboczem ujemnym: 1 → 0 |

Przemysł elektroniczny produkuje gotowe układy scalone zawierające przerzutniki D wyzwalane zboczem dodatnim (przejście sygnału zegarowego z 0 na 1). Często przerzutniki te wyposaża się w dodatkowe dwa wejścia:

Dla wymienionych wejść obowiązują stany zabronione, jak dla przerzutnika S-R (po prostu człon SLAVE jest zwykle realizowany jako przerzutnik SR).

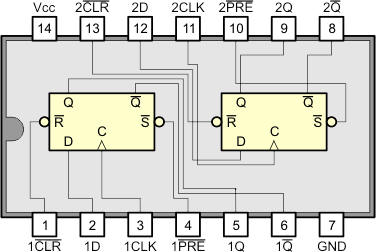

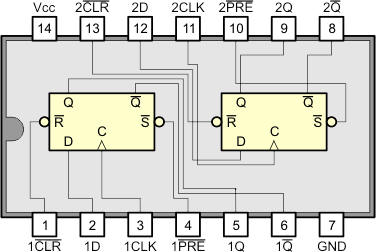

Poniżej przedstawiamy układ scalony SN7474 zawierający dwa przerzutniki D wyzwalane zboczem narastającym (dodatnim) sygnału zegarowego C. W tabelce stanów kolorem czerwonym zaznaczyliśmy stan zabroniony sygnałów wejściowych.

|

SN7474

– dwa przerzutniki D wyzwalane zboczem |

|

||||||||||||||||||||||||||||||||||||||||||||||||

| Przerzutnik T z przerzutnika D  |

|

Działanie powyższego układu opiera się na tym, iż do wejścia danych D jest zawsze doprowadzany sygnał o stanie przeciwnym niż panuje na wyjściu Q. Jeśli teraz sygnał zegarowy aktywuje przerzutnik, to na jego wyjściu Q pojawi się stan przeciwny przeniesiony z wejścia D. Zatem przy każdej aktywacji przerzutnika wejściem zegarowym C jego stan zmienia się na przeciwny.

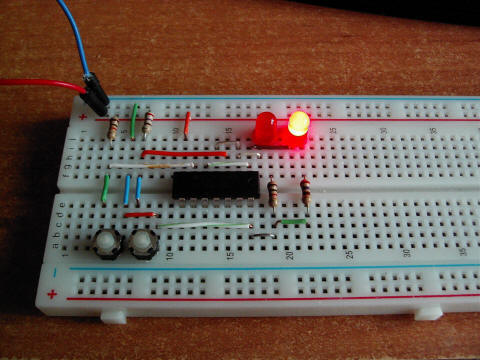

Jako ćwiczenie zbudujemy przerzutnik T z przerzutnika D wyzwalanego zboczem dodatnim (SN7474). Na płytce stykowej zmontuj poniższy układ:

SN7474

– dwa przerzutniki D wyzwalane zboczem dodatnim |

BC547 npn |

Spis elementów:

|

|

|

Układ działa następująco:

Gdy zostanie włączone zasilanie, kondensator 100nF będzie ładowany poprzez opornik 4,7k. Napięcie na kondensatorze będzie rosło, aż osiągnie poziom przewodzenia złącza baza-emiter tranzystora. W takim stanie tranzystor jest otwarty i przewodzi prąd na złączu kolektor-emiter. Powoduje to podawanie stanu niskiego 0 na wejście C przerzutnika.Gdy naciśniemy przycisk, to kondensator będzie się rozładowywał poprzez opornik 100Ω i napięcie na nim spadnie poniżej 0,6V (do około 0,1V, co wymusi dzielnik z oporników 4,1k i 100Ω). Spowoduje to zablokowanie tranzystora i wzrost napięcia na złączu kolektor-emiter. W efekcie na wejście C przerzutnika zostanie podany poziom wysoki i przerzutnik przełączy się w stan przeciwny. Kondensator i oporniki na wejściu mają za zadanie zniwelować drgania styków przełącznika. Dzięki kondensatorowi krótka przerwa w zwarciu nie spowoduje nagłego wzrostu napięcia na kondensatorze, ponieważ musi się on naładować (jeśli tego nie rozumiesz, to wróć do rozdziału o kondensatorach lub o tranzystorach). Z kolei tranzystor ma za zadanie odwrócić poziom niski, który wymusi przełącznik, na poziom wysoki. Pełni on zatem funkcję prymitywnego inwertera.

Każde naciśnięcie przycisku zmienia stan wyjścia Q przerzutnika na przeciwny. Dioda zapala się, a po ponownym naciśnięciu przycisku gaśnie. Przerzutnik D zamienia się w przerzutnik T.

Przerzutnik posiada dwa wejścia sterujące J i K (litery te wybrano arbitralnie jako dwie kolejne litery alfabetu), jedno wejście zegarowe C oraz dwa komplementarne wyjścia Q i Q. Niektóre rozbudowane wersje tego przerzutnika posiadają dodatkowo dwa asynchroniczne wejścia PRESET (ustawia Q na 1) oraz CLEAR (ustawia Q na 0).

Poniżej umieściliśmy symulację sieci logicznej przerzutnika J-K zbudowanego z bramek NAND.

|

|

Przerzutnik J-K jest rozbudowanym przerzutnikiem S-R, do którego dodajemy dodatkowy człon z dwóch bramek sterujący sygnałami na wejściach S i R. Zadaniem tego członu jest uniemożliwienie wysterowania końcowego przerzutnika S-R sygnałami zabronionymi. Uzyskujemy to sprzęgając wejście S z wyjściem Q oraz wejście R z wyjściem Q. Ponieważ wyjścia Q i Q są komplementarne (o stanach przeciwnych), nigdy nie dojdzie do sytuacji, w której oba wejścia S i R znajdą się w stanie niskim.

Przeanalizujmy pracę przerzutnika J-K.

Aby pozbyć się kłopotów z doborem czasu trwania impulsu zegarowego (ważne tylko dla J = K = 1), często stosuje się przerzutnik J-K Master/Slave, który jest wyzwalany zboczem sygnału zegarowego, zatem nie wystąpią w nim problemy ze wzbudzaniem się układu. Poniżej przedstawiamy symulację przykładowej sieci logicznej przerzutnika J-K Master/Slave:

|

|

Dokonajmy analizy pracy powyższego układu.

Zwróć uwagę, iż zastosowanie układu Master/Slave spowodowało, iż sygnał zegarowy nie musi być ograniczany czasowo. Wyzwalanie przerzutnika następuje tylko w momencie przejścia tego sygnału ze stanu 1 na 0. Natomiast czas pomiędzy kolejnymi zboczami sygnału zegarowego może być dowolnie długi.

Przemysł elektroniczny produkuje cyfrowe układy scalone zawierające różne wersje przerzutników J-K. Poniżej podajemy dwa przykładowe układy scalone z przerzutnikami J-K Master/Slave.

|

SN7472 -

przerzutnik J-K MS z ustawianiem i zerowaniem wyzwalany ujemnym zboczem sygnału zegarowego  |

SN7473 -

dwa przerzutniki J-K MS z zerowaniem wyzwalane ujemnym zboczem sygnału zegarowego  |

Zaletą przerzutnika J-K jest jego uniwersalność w prosty sposób można przekształcić go w potrzebny rodzaj przerzutnika.

Pokażemy teraz sposób dokonania konwersji przerzutnika J-K na przerzutnik innych typów. Najpierw utwórzmy tabelkę przejść przerzutnika J-K:

| Wejścia | Wyjścia | ||

| J | K | Qn | Qn+1 |

| 0 | X | 0 | 0 |

| 1 | X | 0 | 1 |

| X | 1 | 1 | 0 |

| X | 0 | 1 | 1 |

Jak odczytujemy tę tabelkę? W pierwszych dwóch kolumnach są stany wejść przerzutnika. X oznacza stan 0 lub 1, czyli dowolny. W zależności od tych stanów zmienia się odpowiednio wyjście Q przerzutnika. Na przykład wiersz 2:

| Wejścia | Wyjścia | ||

| J | K | Qn | Qn+1 |

| 0 | X | 0 | 0 |

| 1 | X | 0 | 1 |

| X | 1 | 1 | 0 |

| X | 0 | 1 | 1 |

Jeśli na wejściu J będzie stan wysoki 1, a na wyjściu Q będzie stan niski 0, to po przełączeniu sygnałem zegarowym na wyjściu Q ustali się stan wysoki 1. Stan wejścia K jest tu obojętny.

Teraz w podobny sposób utworzymy tabelkę przejść dla przerzutnika S-R:

| Wejścia | Wyjścia | ||

| S | R | Qn | Qn+1 |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | zabronione | |

Teraz łączymy obie tabelki przerzutników S-R i J-K, dopisując do tabelki przerzutnika S-R dwie kolumny dla sygnałów J i K:

| S | R | Qn | Qn+1 | J | K |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 | ||

| 0 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 0 | ||

| 1 | 0 | 0 | 1 | ||

| 1 | 0 | 1 | 1 | ||

| 1 | 1 | zabronione | |||

Do kolumn J i K przepisujemy stany wejść przerzutnika J-K z jego tabelki, dla których wyjście Q zmienia się w ten sam sposób. Na przykład w wierszu pierwszym wyjście Q ze stanu 0 przechodzi w ten sam stan 0, zatem:

|

→ |

|

→ |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Postępujemy podobnie z pozostałymi wierszami, otrzymując tabelkę przejścia:

| S | R | Qn | Qn+1 | J | K |

| 0 | 0 | 0 | 0 | 0 | X |

| 0 | 0 | 1 | 1 | X | 0 |

| 0 | 1 | 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 | X | 1 |

| 1 | 0 | 0 | 1 | 1 | X |

| 1 | 0 | 1 | 1 | X | 0 |

| 1 | 1 | zabronione | X | X | |

Stanem zabronionym przerzutnika S-R nie przejmujemy się, ponieważ nie wolno mu go ustawiać.

W następnym kroku musimy ustalić funkcję przejścia z sygnałów S i R na sygnały J i K. Wykorzystamy mapy Karnaugha. Sygnałami wejściowymi będą S, R i Q, a wartością funkcji mają być sygnały J i K.

Dla J J = S |

Dla K K = R |

Jak widzisz, nie musimy nic zmieniać. Przerzutnik J-K może bezpośrednio pełnić w układzie rolę przerzutnika S-R. Otrzymujemy zatem:

Postępujemy identycznie jak dla przerzutnika S-R. Tabelka przejść przerzutnika J-K:

| J | K | Qn | Qn+1 |

| 0 | X | 0 | 0 |

| 1 | X | 0 | 1 |

| X | 1 | 1 | 0 |

| X | 0 | 1 | 1 |

Tabelka przejść przerzutnika D:

| D | Qn | Qn+1 |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Łączymy tabelki, tak aby zgadzały się przejścia sygnału Q:

| D | Qn | Qn+1 | J | K |

| 0 | 0 | 0 | 0 | X |

| 0 | 1 | 0 | X | 1 |

| 1 | 0 | 1 | 1 | X |

| 1 | 1 | 1 | X | 0 |

Tworzymy mapy Karnaugha dla sygnałów J, K w funkcji wejść D i Q:

Dla J J = D |

Dla K K = D |

I ostatecznie:

Tabelka przejść dla przerzutnika J-K:

| J | K | Qn | Qn+1 |

| 0 | X | 0 | 0 |

| 1 | X | 0 | 1 |

| X | 1 | 1 | 0 |

| X | 0 | 1 | 1 |

Tabelka przejść dla przerzutnika T:

| T | Qn | Qn+1 |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Oryginalny przerzutnik T posiada jedno wejście T. Gdy wejście T jest w stanie niskim, to przerzutnik nie zmienia swojego stanu. Gdy wejście T jest w stanie wysokim, to przy każdym zboczu opadającym sygnału zegarowego stan wyjściowy przerzutnika zmienia się na przeciwny.

Łączymy tabelki:

| T | Qn | Qn+1 | J | K |

| 0 | 0 | 0 | 0 | X |

| 0 | 1 | 1 | X | 0 |

| 1 | 0 | 1 | 1 | X |

| 1 | 1 | 0 | X | 1 |

Tworzymy mapy Karnaugha dla sygnałów J i K w funkcji T i Q:

Dla J J = T |

Dla K K = T |

Otrzymujemy:

Zwróć uwagę, że podana tutaj metoda pozwala przekształcić przerzutnik dowolnego typu na przerzutnik innego typu. Wyjściowym przerzutnikiem wcale nie musi być przerzutnik J-K. Spróbuj przekształcić za jej pomocą przerzutnik S-R w przerzutniki D i T.

Do czego możemy potrzebować przerzutników monostabilnych? Zastosowań jest bardzo dużo. Na przykład generacja impulsu o określonym czasie trwania:

Na wejście wyzwalające przerzutnika monostabilnego podajemy impuls. Dodatnie zbocze impulsu powoduje wytrącenie przerzutnika ze stanu równowagi (stan niski 0) i na wyjściu pojawia się stan wysoki 1. Po upływie czasu T przerzutnik powraca samoczynnie do stanu równowagi i na jego wyjściu ponownie pojawia się stan niski 0.

Przerzutnik monostabilny można zbudować z bramek NAND/NOR. Rozważmy dla przykładu działanie poniższego układu:

Układ składa się z dwóch bramek NAND, kondensatora C i opornika R. Jeśli na wejściu We panuje stan wysoki, który jest stanem neutralnym, to układ jest w stanie stabilnym, a na wyjściu również panuje stan wysoki:

Dlaczego tak jest, zrozumiesz za chwilę. Na razie przyjmij ten fakt do wiadomości. W stanie stabilnym kondensator C jest rozładowany.

Teraz na wejście układu podajemy stan niski. Zgodnie z tabelką dla bramki NAND jeśli jedno z wejść ma stan niski, to na wyjściu bramki panuje stan wysoki. Zatem podanie stanu niskiego na wejście układu wymusi stan wysoki bramki b1. Ponieważ kondensator jest rozładowany, to panuje na nim napięcie 0V (jeśli tego nie rozumiesz, przeczytaj rozdział o pojemności). Zgodnie z prawami elektrycznymi na wejściach bramki b2 pojawi się stan wysoki 1. Bramka b2 pełni funkcję inwertera, zatem na jej wyjściu pojawi się stan niski 0:

Jeśli We wróci do stanu 1, to na wyjściu bramki b1 wciąż będzie panował stan 1, ponieważ jej drugie wejście jest zasilane z inwertera b2 stanem 0:

Co się teraz dzieje wewnątrz układu? Ponieważ wyjście bramki b1 jest połączone z wejściami inwertera b2 przez kondensator C, a ten jest połączony poprzez opornik R z masą, to kondensator C zaczyna się ładować przez opornik i napięcie na nim wzrasta. Jeśli rośnie napięcie na kondensatorze, to na wejściach inwertera b2 napięcie zaczyna spadać, ponieważ kondensator "kradnie" go coraz więcej w miarę ładowania się z napięcia wyjściowego bramki b1:

W pewnym momencie napięcie na wejściach inwertera b2 spadnie do poziomu niskiego 0. Inwerter na swoim wyjściu umieści stan 1, który przeniesie się do wejścia bramki b1, co spowoduje z kolei przełączenie jej wyjścia w stan niski 0. Kondensator rozładuje się poprzez opornik R i układ pozostanie już w tym stanie, aż ponownie zostanie wzbudzony niskim napięciem na wejściu We:

Czas trwania impulsu wyjściowego zależy od wartości pojemności C, oporności R oraz typu zastosowanych bramek NAND (inne czasy są dla serii standardowej, a inne dla serii 74LS/74HCT...).

Przemysł elektroniczny produkuje gotowe przerzutniki monostabilne w postaci układów scalonych, np:

Układy te posiadają dobrze zdefiniowane czasy trwania impulsu wyjściowego, co pozwala uzyskiwać powtarzalne wyniki. Co więcej czas impulsu można w nich regulować przez dołączenie zewnętrznego opornika i kondensatora.

|

Zespół Przedmiotowy Chemii-Fizyki-Informatyki w I Liceum Ogólnokształcącym im. Kazimierza Brodzińskiego w Tarnowie ul. Piłsudskiego 4 ©2024 mgr Jerzy Wałaszek |

Materiały tylko do użytku dydaktycznego. Ich kopiowanie i powielanie jest dozwolone

pod warunkiem podania źródła oraz niepobierania za to pieniędzy.

Pytania proszę przesyłać na adres email:

Serwis wykorzystuje pliki cookies. Jeśli nie chcesz ich otrzymywać, zablokuj je w swojej przeglądarce.

Informacje dodatkowe.